## **W7100A Datasheet**

Version 1.2.4

© 2013~2014 WIZnet Co.,Ltd. All Rights Reserved. For more information, visit our website at <a href="http://www.wiznet.co.kr">http://www.wiznet.co.kr</a>

# **Table of Contents**

| 1        | Overview | ······································   | 11 |

|----------|----------|------------------------------------------|----|

| 1.1      | Intro    | duction                                  | 11 |

| 1.2      | W710     | 0A Features                              | 11 |

| 1.3      | W710     | OA Block Diagram & Features              | 12 |

|          | 1.3.1    | ALU (Arithmetic Logic Unit)              | 12 |

|          | 1.3.2    | TCPIPCore                                | 14 |

| 1.4      | Pin D    | escription                               | 16 |

|          | 1.4.1    | Pin Layout                               | 16 |

|          | 1.4.2    | Pin Description                          | 17 |

| 1.4.2.1  |          | Configuration                            | 18 |

| 1.4.2.2  |          | Timer                                    | 18 |

| 1.4.2.3  |          | UART                                     | 19 |

| 1.4.2.4  |          | DoCD™ Compatible Debugger                | 19 |

| 1.4.2.5  |          | Interrupt / Clock                        | 19 |

| 1.4.2.6  |          | GPIO                                     | 20 |

| 1.4.2.7  |          | External Memory Interface                | 21 |

| 1.4.2.8  |          | Media Interface                          | 21 |

| 1.4.2.9  |          | Network Indicator LED                    | 21 |

| 1.4.2.10 | )        | Power Supply Signal                      | 22 |

| 1.5      | 64pin    | package description                      | 24 |

|          | 1.5.1    | Difference between 100 and 64pin package | 24 |

| 2        | Memory   |                                          | 25 |

| 2.1      | Code     | Memory                                   | 26 |

|          | 2.1.1    | Code Memory Wait States                  | 28 |

| 2.2      | Data     | Memory                                   | 28 |

|          | 2.2.1    | Data Memory Wait States                  | 28 |

| 2.3      | Exter    | nal Data Memory Access                   | 28 |

|          | 2.3.1    | Standard 8051 Interface                  | 29 |

|          | 2.3.2    | Direct Interface                         | 30 |

| 2.4      | Interr   | nal Data Memory and SFR                  | 31 |

| 2.5      | SFR d    | efinition                                | 32 |

|          | 2.5.1    | Program Code Memory Write Enable Bit     | 32 |

|          | 2.5.2    | Program Code Memory Wait States Register | 33 |

|          | 2.5.3    | Data Pointer Extended Registers          | 34 |

|          | 2.5.4    | Data Pointer Registers                   | 35 |

|          | 2.5.5    | Clock Control Register                   | 36 |

|   | 2.5.6     | Internal Memory Wait States Register                           | 37 |

|---|-----------|----------------------------------------------------------------|----|

|   | 2.5.7     | Address Latch Enable Register                                  | 38 |

|   | 2.5.8     | External Memory Wait States Register                           | 38 |

|   | 2.5.9     | Stack Pointer                                                  | 38 |

|   | 2.5.1     | 0 New & Extended SFR                                           | 38 |

|   | 2.5.1     | 1 Peripheral Registers                                         | 41 |

| 3 | Interrupt | t                                                              | 42 |

| 4 | I/O Ports | 5                                                              | 46 |

| 5 | Timers    |                                                                | 50 |

|   | 5.1 Time  | ers 0, 1                                                       | 50 |

|   | 5.1.1     | Overview                                                       | 50 |

|   | 5.1.2     | Interrupts                                                     | 51 |

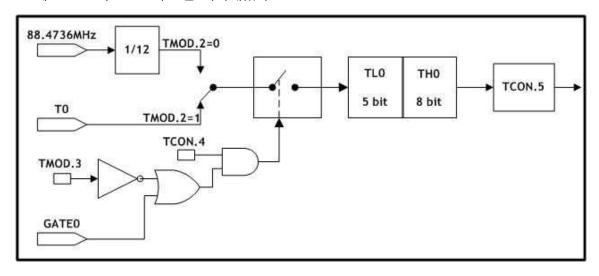

|   | 5.1.3     | Timer0 - Mode0                                                 | 52 |

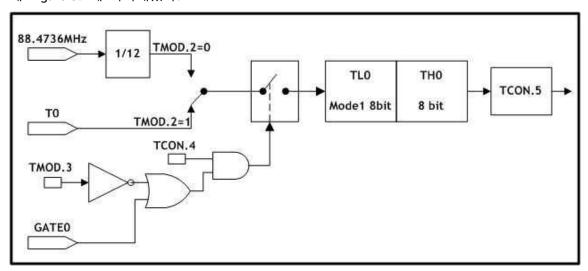

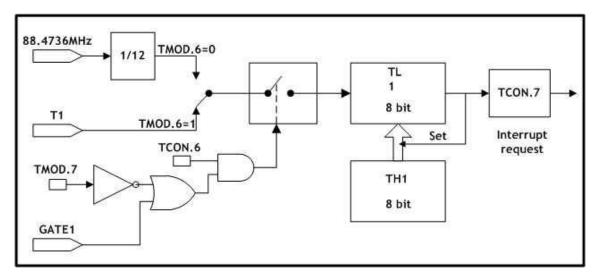

|   | 5.1.4     | Timer0 - Mode1                                                 | 53 |

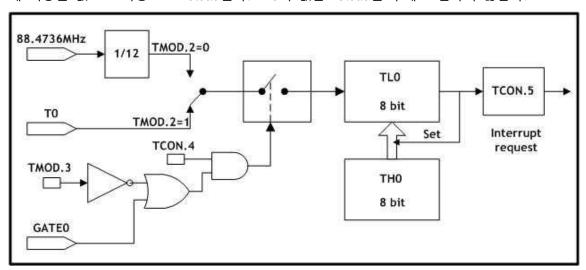

|   | 5.1.5     | Timer0 - Mode2                                                 | 53 |

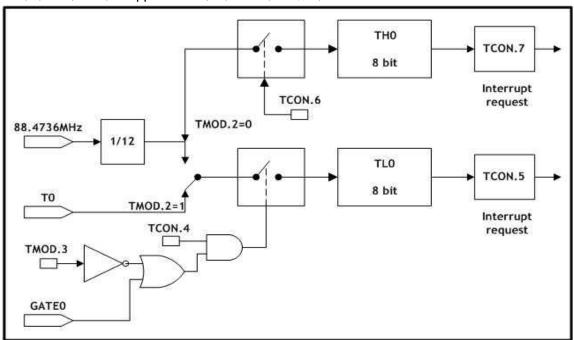

|   | 5.1.6     | Timer0 - Mode3                                                 | 53 |

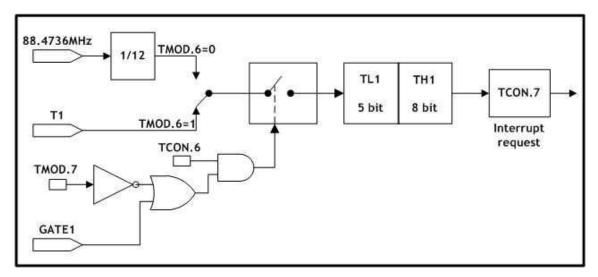

|   | 5.1.7     | Timer1 - Mode0                                                 | 54 |

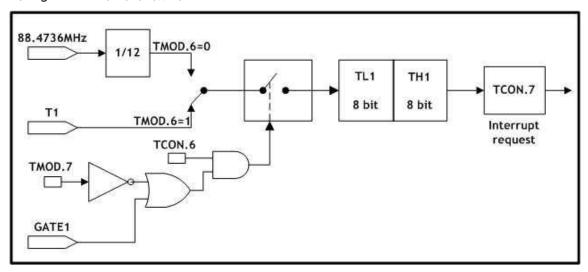

|   | 5.1.8     | Timer1 - Mode1                                                 | 55 |

|   | 5.1.9     | Timer1 - Mode2                                                 | 55 |

|   | 5.1.1     | 0 Timer1 - Mode3                                               | 56 |

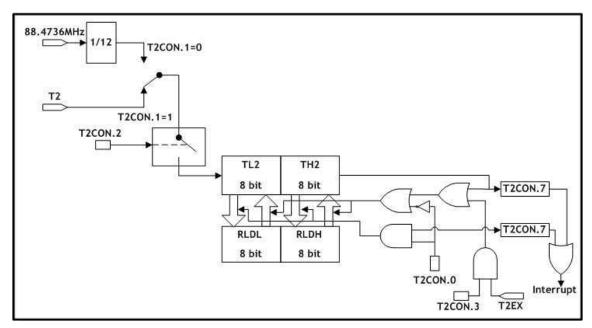

|   | 5.2 Time  | er2                                                            | 56 |

|   | 5.2.1     | Overview                                                       | 56 |

|   | 5.2.2     | Interrupts                                                     | 58 |

| 6 | UART      |                                                                | 61 |

|   | 6.1 Inter | rrupts                                                         | 62 |

|   | 6.2 Mod   | e0, Synchronous                                                | 63 |

|   | 6.3 Mod   | e 1, 8-Bit UART, Variable Baud Rate, Timer 1 or 2 Clock Source | 64 |

|   | 6.4 Mod   | e 2, 9-Bit UART, Fixed Baud Rate                               | 64 |

|   | 6.5 Mod   | e 3, 9-Bit UART, Variable Baud Rate, Timer1 or 2 Clock Source  | 64 |

|   | 6.6 Exar  | nples of Baud Rate Setting                                     | 65 |

| 7 | Watchdo   | g Timer                                                        | 66 |

|   | 7.1 Over  | rview                                                          | 66 |

|   | 7.2 Inter | rrupts                                                         | 66 |

|   | 7.3 Wate  | chdog Timer Reset                                              | 67 |

|   | 7.4 Simp  | ole Timer                                                      | 68 |

|   | 7.5 Syste | em Monitor                                                     | 68 |

|   | 7.6 Wate  | chdog Related Registers                                        | 68 |

|   | 7.7 Wate  | chdog Control                                                  | 69 |

|     |      | 7.7.1    | Clock Control                          | 70  |

|-----|------|----------|----------------------------------------|-----|

|     | 7.8  | Timed    | d Access Registers                     | 70  |

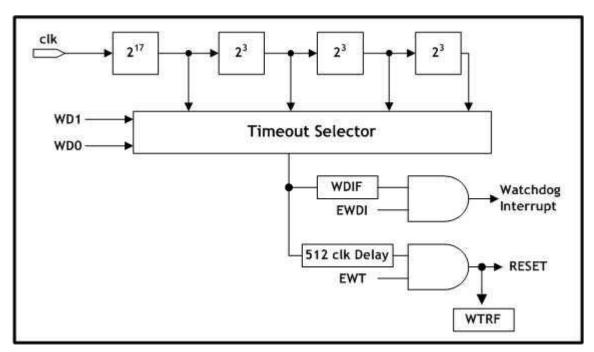

| 8   | TC   | PIPCore  | e                                      | 72  |

|     | 8.1  | Memo     | ory Map                                | 72  |

|     | 8.2  | Regist   | ters list                              | 72  |

|     |      | 8.2.1    | Common Registers                       | 72  |

|     |      | 8.2.2    | SOCKET Registers                       | 74  |

|     | 8.3  | Regist   | ter Description                        | 85  |

|     |      | 8.3.1    | Common Register                        | 85  |

|     |      | 8.3.2    | SOCKET Registers                       | 91  |

| 9   | Fu   | ınctiona | l Description                          | 108 |

|     | 9.1  | Initia   | lization                               | 108 |

|     | 9.2  | Data     | Communication                          | 113 |

|     |      | 9.2.1    | TCP                                    | 113 |

| 9.2 | .1.1 |          | TCP SERVER                             | 114 |

| 9.2 | .1.2 |          | TCP CLIENT                             | 120 |

|     |      | 9.2.2    | UDP                                    | 121 |

| 9.2 | .2.1 |          | Unicast & Broadcast                    | 121 |

| 9.2 | .2.2 |          | Multicast                              | 126 |

|     |      | 9.2.3    | IPRAW                                  | 129 |

|     |      | 9.2.4    | MACRAW                                 | 131 |

| 10  | El   | ectrical | Specification                          | 138 |

|     | 10.1 | Absol    | ute Maximum Ratings                    | 138 |

|     | 10.2 | DC Cł    | haracteristics(Input, Output, I/O)     | 138 |

|     | 10.3 | Powe     | r consumption(Driving voltage 3.3V)    | 139 |

|     | 10.4 | AC Ch    | naracteristics                         | 139 |

|     | 10.5 | Crysta   | al Characteristics                     | 140 |

|     | 10.6 | Trans    | former Characteristics                 | 140 |

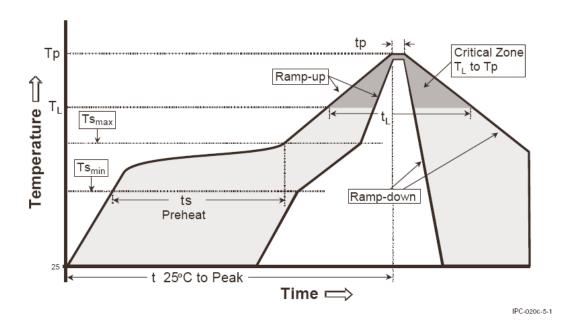

| 11  | IR   | Reflow   | Temperature Profile (Lead-Free)        | 141 |

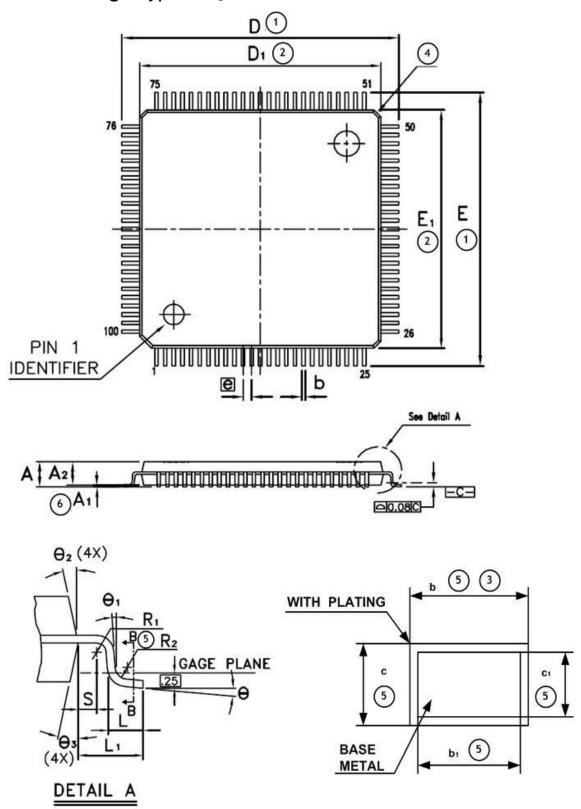

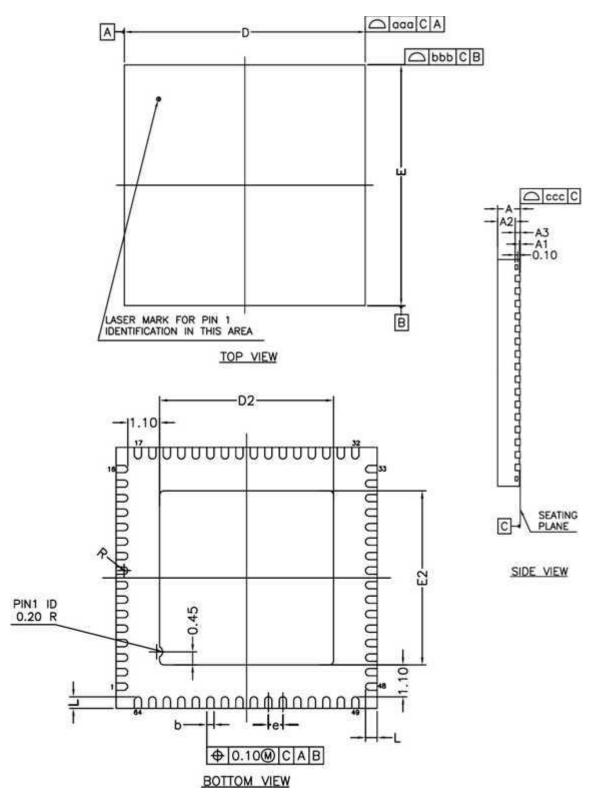

| 12  | Pa   | ckage D  | Descriptions                           | 142 |

|     | 12.1 | Packa    | age type: LQFP 100                     | 142 |

|     | 12.2 | Packa    | age type: QFN 64                       | 144 |

| 13  | Ap   | pendix:  | : Performance Improvement about W7100A | 146 |

|     | 13.1 | Summ     | nary                                   | 146 |

|     | 13.2 | 8-Bit    | Arithmetic Functions                   | 146 |

|     |      | 13.2.1   | Addition                               | 146 |

|     |      | 13.2.2   | Subtraction                            | 147 |

|     |      | 13.2.3   | Multiplication                         | 148 |

|      | 13.2.4 Division             | 149 |

|------|-----------------------------|-----|

| 13.3 | 16-Bit Arithmetic Functions | 149 |

|      | 13.3.1 Addition             | 149 |

|      | 13.3.2 Subtraction          | 150 |

|      | 13.3.3 Multiplication       | 150 |

| 13.4 | 32-bit Arithmetic Functions | 151 |

|      | 13.4.1 Addition             | 151 |

|      | 13.4.2 Subtraction          | 151 |

|      | 13.4.3 Multiplication       | 152 |

# **List of Figures**

| Figure 1.1 W7100A Block Diagram                                                      |

|--------------------------------------------------------------------------------------|

| Figure 1.2 Accumulator A Register                                                    |

| Figure 1.3 B Register                                                                |

| Figure 1.4 Program Status Word Register                                              |

| Figure 1.5 PSW Register                                                              |

| Figure 1.6 TCPIPCore Block Diagram                                                   |

| Figure 1.7 W7100A Pin Layout                                                         |

| Figure 1.8 W7100A QFN 64 Pin Layout                                                  |

| Figure 1.9 Power Design                                                              |

| Figure 2.1 Code / Data Memory Connections                                            |

| (Example ICs: MAX811, MIC811, DS1811)                                                |

| Figure 2.2. Boot Sequence Flowchart                                                  |

| Figure 2.3 APP Entry Process                                                         |

| Figure 2.4 Changing the code memory Status at <b>RB</b> = '0'                        |

| Figure 2.5 "Data Memory" Map                                                         |

| Figure 2.6 Standard 8051 External Pin Access Mode (EM[2:0] = "001")                  |

| Figure 2.7 Standard 8051 External Pin Access Mode (EM[2:0] = "011")                  |

| Figure 2.8 Direct 8051 External Pin Access Mode (EM[2:0] = "101")                    |

| Figure 2.9 Direct 8051 External Pin Access Mode (EM[2:0] = "111")                    |

| Figure 2.10 Internal Memory Map                                                      |

| Figure 2.11 SFR Memory Map                                                           |

| Figure 2.12 PWE bit of PCON Register                                                 |

| Figure 2.13 Code memory Wait States Register                                         |

| Figure 2.14 Waveform for code memory Synchronous Read Cycle with Minimal Wait States |

| (WTST = '4')                                                                         |

| Figure 2.15 Waveform for code memory Synchronous Write Cycle with Minimal Wait       |

| States(WTST = '4')                                                                   |

| Figure 2.16 Data Pointer Extended Register                                           |

| Figure 2.17 Data Pointer Extended Register                                           |

| Figure 2.18 MOVX @RI Extended Register                                               |

| Figure 2.19 Data Pointer Register DPTR0                                              |

| Figure 2.20 Data Pointer 1 Register DPTR1                                            |

| Figure 2.21 Data Pointer Select Register                                             |

| Figure 2.22 Clock Control Register - STRETCH bits                                    |

| Figure 2.23 Internal Memory Wait States Register                                     |

| Figure 2.24 Address Latch Enable Control register                                    |

| Figure 2.25 First Byte of Internal Memory Wait States Register  | . 38 |

|-----------------------------------------------------------------|------|

| Figure 2.26 Second Byte of Internal Memory Wait States Register | . 38 |

| Figure 2.27 Stack Pointer Register                              | . 38 |

| Figure 2.28 PHY Status Register                                 | . 39 |

| Figure 2.29 Internal PHY Configuration Register                 | . 39 |

| Figure 2.30 W7100A Configuration Register                       | 40   |

| Figure 2.31 Core clock count register                           | 40   |

| Figure 2.32 Core clock count register                           | 40   |

| Figure 2.33 Core clock count register                           | 40   |

| Figure 2.34 Core clock count register                           | . 41 |

| Figure 3.1 Interrupt Enable Register                            | 43   |

| Figure 3.2 Interrupt Priority Register                          | 43   |

| Figure 3.3 Timer 0, 1 Configuration Register                    | 43   |

| Figure 3.4 UART Configuration Register                          | . 44 |

| Figure 3.5 Extended Interrupt Enable Register                   | . 44 |

| Figure 3.6 Extended Interrupt Priority Register                 | . 44 |

| Figure 3.7 Extended Interrupt Flag Register                     | 45   |

| Figure 3.8 Watchdog Control Register                            | 45   |

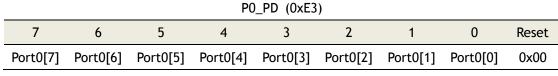

| Figure 4.1 Port0 Pull-down register                             | 46   |

| Figure 4.2 Port0 Register                                       | 46   |

| Figure 4.3 Port1 Register                                       | 46   |

| Figure 4.4 Port2 Register                                       | 47   |

| Figure 4.5 Port3 Register                                       | 47   |

| Figure 4.6 Port0 Pull-down register                             | 48   |

| Figure 4.7 Port1 Pull-down register                             | 48   |

| Figure 4.8 Port2 Pull-down register                             | 48   |

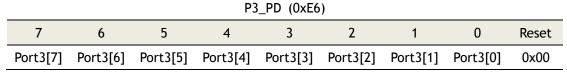

| Figure 4.9 Port3 Pull-down register                             | 48   |

| Figure 4.10 Port0 Pull-up register                              | 48   |

| Figure 4.11 Port1 Pull-up register                              | 49   |

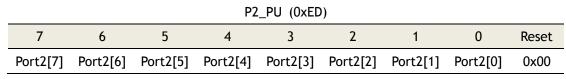

| Figure 4.12 Port2 Pull-up register                              | 49   |

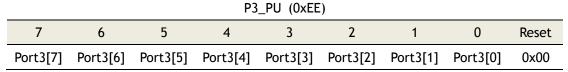

| Figure 4.13 Port3 Pull-up register                              | 49   |

| Figure 5.1 Timer 0, 1 Control Mode Register                     | . 50 |

| Figure 5.2 Timer 0, 1 Configuration Register                    | . 51 |

| Figure 5.3 Interrupt Enable Register                            | . 51 |

| Figure 5.4 Interrupt Priority Register                          | . 51 |

| Figure 5.5 Timer 0, 1 Configuration Register                    | . 52 |

| Figure 5.6 Timer Counter0, Mode0: 13-Bit Timer/Counter          | . 52 |

| Figure 5.7 Timer/Counter0, Mode1: 16-Bit Timer/Counter          | 53   |

| Figure 5.8 Timer/Counter0, Mode2: 8-Bit Timer/Counter with Auto-Reload    | 53  |

|---------------------------------------------------------------------------|-----|

| Figure 5.9 Timer/Counter0, Mode3: Two 8-Bit Timers/Counters               | 54  |

| Figure 5.10 Timer/Counter1, Mode0: 13-Bit Timer/Counter                   | 55  |

| Figure 5.11 Timer/Counter1, Mode1: 16-Bit Timers/Counters                 | 55  |

| Figure 5.12 Timer/Counter1, Mode2: 8-Bit Timer/Counter with Auto-Reload   | 56  |

| Figure 5.13 Timer2 Configuration Register                                 | 57  |

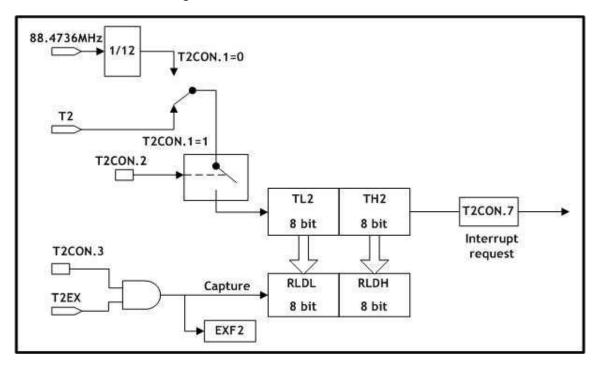

| Figure 5.14 Timer/Counter2, 16-Bit Timer/Counter with Auto-Reload         | 58  |

| Figure 5.15 Interrupt Enable Register — Timer2                            | 58  |

| Figure 5.16 Interrupt Priority Register — Timer2                          | 58  |

| Figure 5.17 Timer2 Configuration Register — TF2                           | 58  |

| Figure 5.18 Timer/Counter2, 16-Bit Timer/Counter with Capture Mode        | 59  |

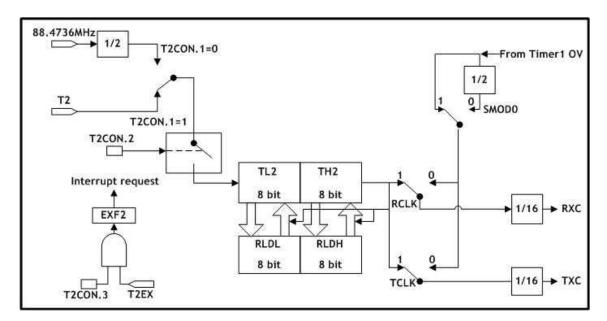

| Figure 5.19 Timer2 for Baud Rate Generator Mode                           | 60  |

| Figure 6.1 UART Buffer Register                                           | 61  |

| Figure 6.2 UART Configuration Register                                    | 61  |

| Figure 6.3 UART Bits in Power Configuration Register                      | 62  |

| Figure 6.4 UART Bits in Interrupt Enable Register                         | 63  |

| Figure 6.5 UART Bits in Interrupt Priority Register                       | 63  |

| Figure 6.6 UART Configuration Register                                    | 63  |

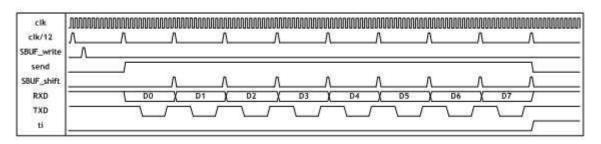

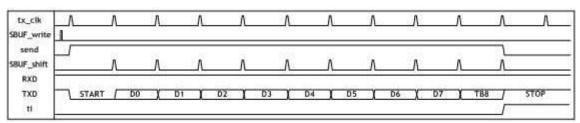

| Figure 6.7 Timing Diagram for UART Transmission Mode0 (clk = 88.4736 MHz) | 63  |

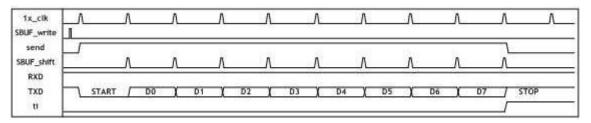

| Figure 6.8 Timing Diagram for UART Transmission Mode1                     | 64  |

| Figure 6.9 Timing Diagram for UART Transmission Mode2                     | 64  |

| Figure 6.10 Timing Diagram for UART Transmission Mode3                    | 64  |

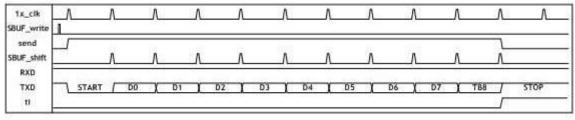

| Figure 7.1 Watchdog Timer Structure                                       | 66  |

| Figure 7.2 Interrupt Enable Register                                      | 66  |

| Figure 7.3 Extended Interrupt Enable Register                             | 67  |

| Figure 7.4 Extended interrupt Priority Register                           | 67  |

| Figure 7.5 Watchdog Control Register                                      | 67  |

| Figure 7.6 Watchdog Control Register                                      | 69  |

| Figure 7.7 Clock Control register - Watchdog bits                         | 70  |

| Figure 8.1 TCPIPCore Memory Map                                           | 72  |

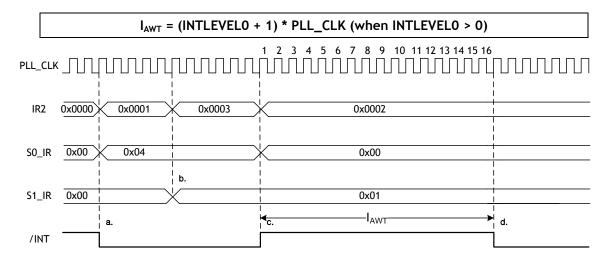

| Figure 8.2 SOCKET <i>n</i> Status transition                              | 99  |

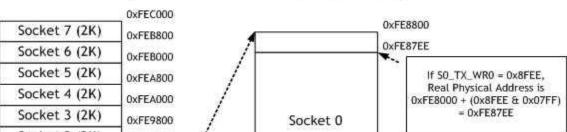

| Figure 8.3 Calculate Physical Address                                     | 105 |

| Figure 9.1 Allocation TX/RX memory of SOCKET n                            | 112 |

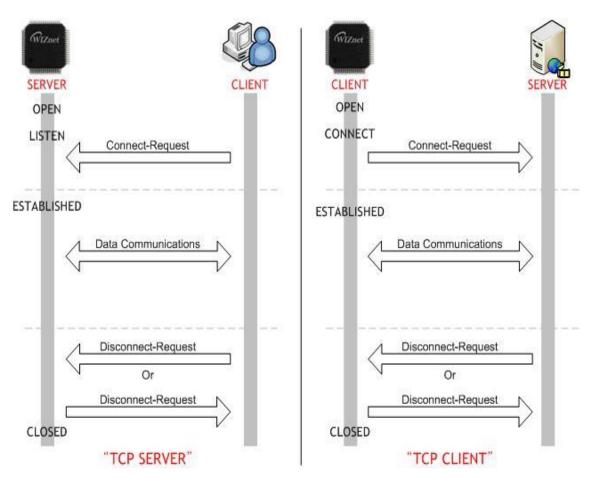

| Figure 9.2 TCP SERVER & TCP CLIENT                                        | 113 |

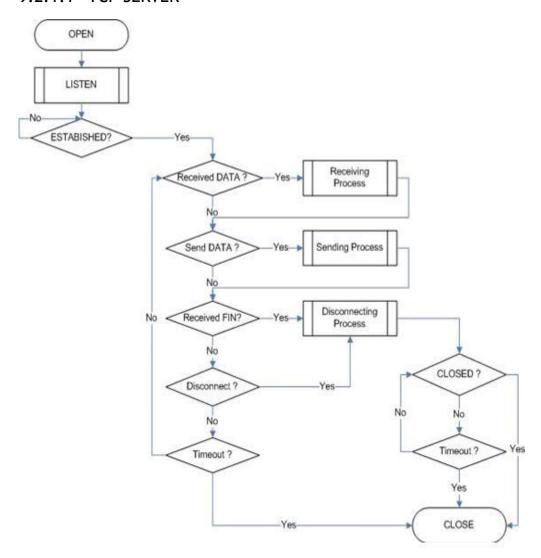

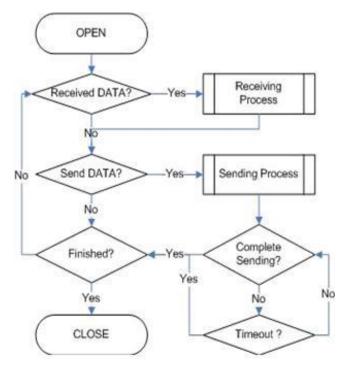

| Figure 9.3 "TCP SERVER" Operation Flow                                    | 114 |

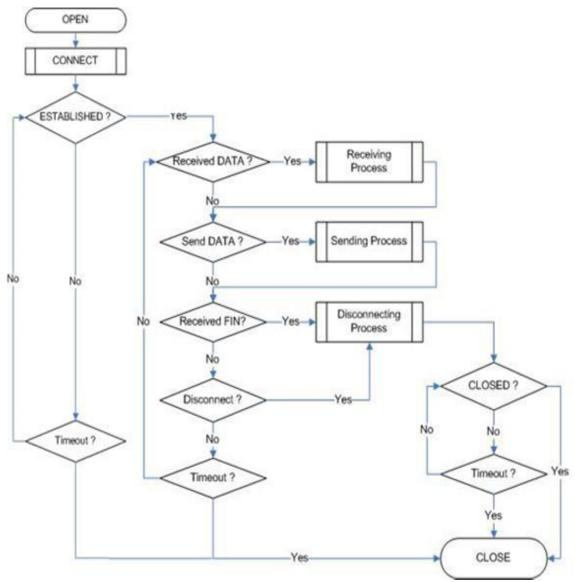

| Figure 9.4 "TCP CLIENT" Operation Flow                                    | 120 |

| Figure 9.5 UDP Operation Flow                                             | 121 |

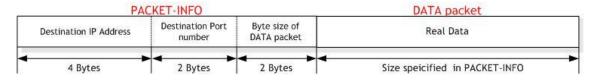

| Figure 9.6 The received UDP data format                                   | 123 |

| Figure 9.7 IPRAW Operation Flow             | 130 |

|---------------------------------------------|-----|

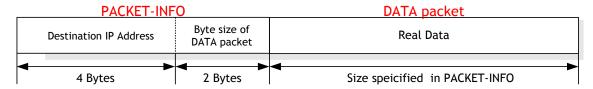

| Figure 9.8 The received IPRAW data format   | 131 |

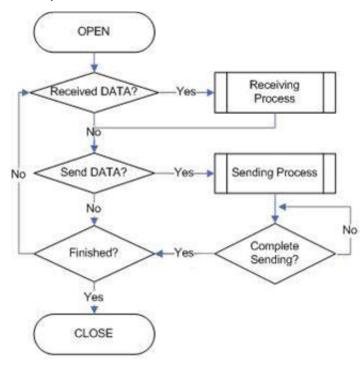

| Figure 9.9 MACRAW Operation Flow            | 132 |

| Figure 9.10 The received MACRAW data format |     |

# **List of Tables**

| Table 2.1 External memory access mode        | 29  |

|----------------------------------------------|-----|

| Table 2.2 WTST Register Values               | 33  |

| Table 2.3 DPTR0, DPTR1 Operations            | 35  |

| Table 2.4 MD[2:0] Bit Values                 | 36  |

| Table 2.5 Ram WTST Bit Values                | 37  |

| Table 2.6 TCPIPCore / Flash WTST Bit Values  | 37  |

| Table 3.1 External Interrupt Pin Description | 42  |

| Table 3.2 W7100A Interrupt Summary           | 42  |

| Table 4.1 I/O Ports Pin Description          | 46  |

| Table 4.2 Read-Modify-Write Instructions     | 47  |

| Table 5.1 Timers 0, 1 Pin Description        | 50  |

| Table 5.2 Timers 0, 1 Mode                   | 50  |

| Table 5.3 Timer0, 1 interrupts               | 52  |

| Table 5.4 Timer2 Pin Description             | 56  |

| Table 5.5 Timer2 Modes                       | 56  |

| Table 5.6 Timer2 Interrupt                   | 59  |

| Table 6.1 UART Pin Description               | 61  |

| Table 6.2 UART Modes                         | 62  |

| Table 6.3 UART Baud Rates                    | 62  |

| Table 6.4 UART Interrupt                     | 63  |

| Table 6.5 Examples of Baud Rate Setting      | 65  |

| Table 7.1 Watchdog Interrupt                 | 67  |

| Table 7.2 Summary for Watchdog Related Bits  | 68  |

| Table 7.3 Watchdog Bits and Actions          | 69  |

| Table 7.4 Watchdog Intervals                 | 70  |

| Table 7.5 Timed Access Registers             | 70  |

| Table 9.1 Timer / Counter Mode               | 109 |

| Table 9.2 Baud rate                          | 109 |

| Table 9.3 Mode of UART                       | 109 |

#### 1 Overview

#### 1.1 Introduction

iMCU W7100A는 8051호환 마이크로 컨트롤러, 64KB SRAM과 hardwired TCP/IP Core 를 내장한 고성능 one-chip 인터넷 솔루션 이다. Hardwired TCP/IP 코어는 Ethernet MAC과 PHY 를 내장한 TCP/IP stack으로서 시장에서 그 성능을 증명해 왔다. Hardwired TCP/IP stack에 포함된 TCP, UDP, IPv4, ICMP, ARP, IGMP 그리고 PPPOE는 수년간 다양한 응용분야에 이용되어 왔다.

#### 1.2 W7100A Features

- Fully software compatible with industrial standard 8051

- $\bullet$  Pipelined architecture which enables execution of instructions 4~5 times faster than a standard 8051

- 10BaseT/100BaseTX Ethernet PHY embedded

- · Power down mode supported for saving power consumption

- Hardwired TCP/IP Protocols: TCP, UDP, ICMP, IPv4 ARP, IGMP, PPPoE, Ethernet

- Auto Negotiation (Full-duplex and half duplex), Auto MDI/MDIX

- · ADSL connection with PPPoE Protocol with PAP/CHAP Authentication mode support

- · 8 independent sockets which are running simultaneously

- · 32Kbytes Data buffer for the Network

- Network status LED outputs (TX, RX, Full/Half duplex, Collision, Link, and Speed)

- Not supports IP fragmentation

- 2 Data Pointers (DPTRs) for fast memory blocks processing

- · Advanced INC & DEC modes

- · Auto-switch of current DPTR

- 64KBytes Data Memory (RAM)

- 255Bytes data FLASH, 64KBytes Code Memory, 2KBytes Boot Code Memory

- Up to 16M bytes of external (off-chip) data memory

- Interrupt controller

- 2 priority levels

- · 4 external interrupt sources

- 1 Watchdog interrupt

- Four 8-bit I/O Ports

- Three timers/counters

- Full-duplex UART

- · Programmable Watchdog Timer

- DoCD™ compatible debugger

- High Product Endurance

- Minimum 100,000 program/erase cycles

- · Minimum 10 years data retention

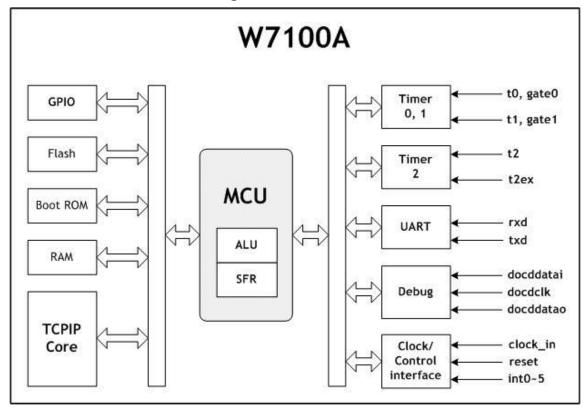

## 1.3 W7100A Block Diagram & Features

Figure 1.1 W7100A Block Diagram

W7100A 내부 블록 다이어그램을 그림1.1에 나타내었다.

**ALU** - 산술, 논리연산을 수행한다. Accumulator (ACC)와 Program Status Word (PSW), B 레지스터, 그리고 arithmetic unit, logic unit, multiplier, divider등 관련된 Logic을 포함하고 있다.

SFR - Special function register를 제어한다. 표준, 사용자 지정 register들과 관련된 logic을 포함하고 있다. 사용자가 정의한 외부 장비를 direct addressing mode 명령을 이용해서 빠르게 access (read, write, modify) 할 수 있다.

## 1.3.1 ALU (Arithmetic Logic Unit)

W7100A는 표준 8051 microcontroller와 완벽하게 호환된다. 그리고 관련된 모든 명령을 포함하고 있다. W7100A는 고속 명령어 수행을 가능하게 하는 많은 구조적 장점을 가지고 있다. W7100A MCU의 ALU는 광범위한 data 처리를 하고 이것은 8-bit ALU, ACC (0xE0) register, B (0xF0) register와 PSW (0xD0) register 로 구성된다.

| ACC (0xE0) |       |       |       |       |       |       |       |       |       |

|------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|            | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | Reset |

|            | ACC.7 | ACC.6 | ACC.5 | ACC.4 | ACC.3 | ACC.2 | ACC.1 | ACC.0 | 0x00  |

Figure 1.2 Accumulator A Register

B register는 곱셈연산과 나눗셈연산 중에 사용된다. 다른 경우에, B register는 보통 SFR처럼 동작한다.

#### B (0xF0)

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | Reset |

|-----|-----|-----|-----|-----|-----|-----|-----|-------|

| B.7 | B.6 | B.5 | B.4 | B.3 | B.2 | B.1 | B.0 | 0x00  |

Figure 1.3 B Register

ALU는 덧셈, 뺄셈, 곱셈, 나눗셈 과 같은 산술연산과 증가 (increment), 감소 (decrement), BCD-decimal-add-adjust, 비교 (compare) 연산 등을 수행한다. 논리 unit은 다른 연산들을 수행하기 위해 AND, OR, Exclusive OR, complement, rotation을 이용한다. Boolean 프로세서는 set, clear, complement, jump-if-not-set, jump-if-set-and-clear 그리고 move to/from carry 와 같은 bit연산을 수행한다.

#### PSW (0xD0)

| 7  | 6  | 5  | 4   | 3   | 2  | 1  | 0 | Reset |

|----|----|----|-----|-----|----|----|---|-------|

| CY | AC | F0 | RS1 | RS0 | OV | F1 | Р | 0x00  |

Figure 1.4 Program Status Word Register

| CY      | Carry flag                           |  |  |  |  |  |  |

|---------|--------------------------------------|--|--|--|--|--|--|

| AC      | Auxiliary carry                      |  |  |  |  |  |  |

| F0      | General purpose flag 0               |  |  |  |  |  |  |

|         | Register bank select bits            |  |  |  |  |  |  |

|         | RS[1:0] Function Description         |  |  |  |  |  |  |

| DC[1.0] | 00 -Bank 0, data address 0x00 - 0x07 |  |  |  |  |  |  |

| RS[1:0] | 01 -Bank 1, data address 0x08 - 0x0F |  |  |  |  |  |  |

|         | 10 -Bank 2, data address 0x10 - 0x17 |  |  |  |  |  |  |

|         | 11 -Bank 3, data address 0x18 - 0x1F |  |  |  |  |  |  |

| OV      | Overflow flag                        |  |  |  |  |  |  |

| F1      | General purpose flag 1               |  |  |  |  |  |  |

| Р       | Parity flag                          |  |  |  |  |  |  |

Figure 1.5 PSW Register

PSW register는 MCU의 현재 상태를 반영할 수 있는 몇몇 bit들을 포함하고 있다.

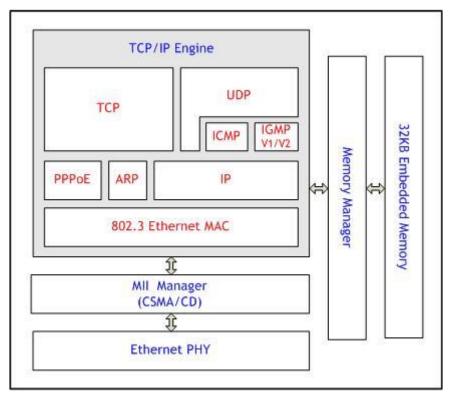

#### 1.3.2 TCPIPCore

Figure 1.6 TCPIPCore Block Diagram

#### **Ethernet PHY**

W7100A는 10BaseT/100BaseTX Ethernet PHY를 내장하고 있다. Half-duplex와 Full-duplex를 모두 지원하며 Auto-negotiation과 Auto-MDI/MDIX를 지원한다. 또한 Link, TX, RX 상태, Collision, Speed와 Duplex 6개의 네트워크 indicator LED 출력을 지원한다.

#### **TCPIP Engine**

TCPIP 엔진은 WIZnet의 네트워크 프로토콜기술을 기반으로 하는 Hardwired logic이다.

802.3 Ethernet MAC(Media Access Control)

CSMA/CD (<u>Carrier Sense Multiple Access with Collision Detect</u>) 을 지원하며 프로토콜은 48-bit source/destination MAC address를 기반으로 하고 있다.

PPPoE(Point-To-Point Protocol over Ethernet)

이 프로토콜은 Ethernet을 통해 PPP서비스를 이용한다. Ethernet 프레임 전송 시에 Payload (PPP 프레임) 를 encapsulate하고, 수신 시에 PPP 프레임을 de-capsulate한다. PPPoE는 PPPoE서버와 PAP/CHAP인증을 이용해서 PPP 통신을 한다.

ARP(Address Resolution Protocol)

ARP는 IP address를 이용한 MAC address resolution protocol이다. 이 프로토콜은 서로 MAC address를 결정하기 위해 ARP-reply와 ARP-request를 교환한다.

- IP (Internet Protocol)

IP 계층 (layer) 에서 동작하며 데이터 통신을 지원한다. IP fragmentation 은 지원하지

않기 때문에 fragmented packet은 수신할 수 없다. TCP나 UDP를 제외한 모든 프로토콜 number를 지원한다. TCP나 UDP의 경우 hardwired embedded TCPIP stack을 지원한다.

#### ICMP(Internet Control Message Protocol)

ICMP는 information, unreachable destination 을 지원하는 프로토콜이다. Ping request ICMP packet이 수신되면, Ping reply ICMP packet을 송신한다.

#### - IGMPv1/v2(Internet Group Management Protocol version 1/2)

IGMP Join/Leave와 같은 IGMP 메시지를 처리하는 프로토콜이다. IGMP는 오직 UDP multicast mode에서만 동작한다. Version 1 과 2 인 IGMP logic만 지원한다. 새로운 버전의 IGMP을 사용하려면, 직접 IGMP를 IP 계층에 구현해야만 한다.

#### UDP(User Datagram Protocol)

UDP계층에서 데이터 통신을 지원하는 프로토콜이다. 사용자는 unicast, multicast, broadcast와 같은 사용자 데이터 그램을 지원한다.

#### - TCP(Transmission Control Protocol)

이 프로토콜은 TCP 계층에서 동작하며 데이터 통신을 지원한다. TCP 서버와 클라이언 트 mode를 지원한다.

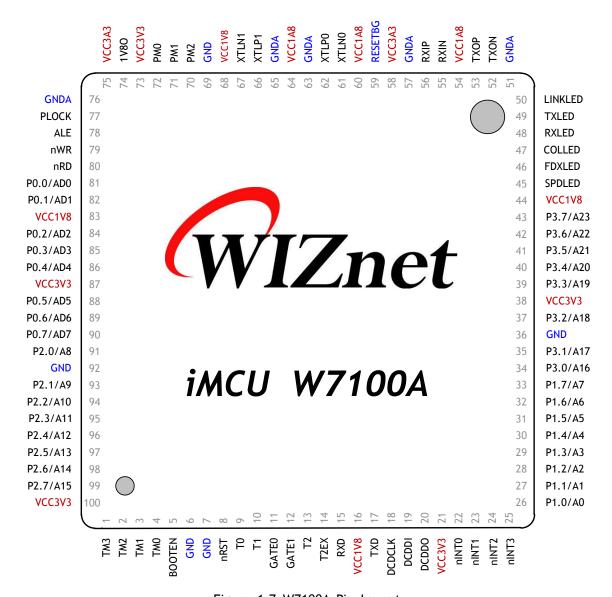

## 1.4 Pin Description

## 1.4.1 Pin Layout

Package type: LQFP 100

Figure 1.7 W7100A Pin Layout

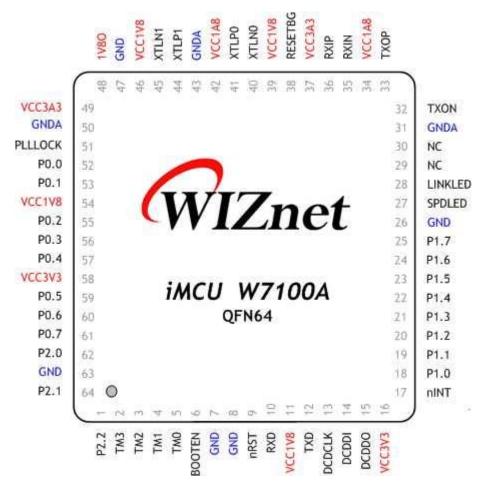

Package type: QFN 64

Figure 1.8 W7100A QFN 64 Pin Layout

## 1.4.2 Pin Description

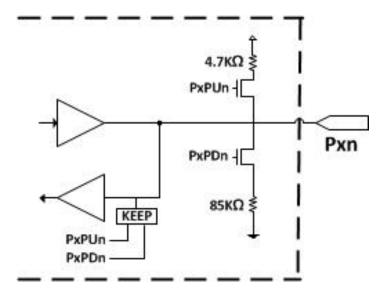

아래 테이블에 Pin 기능들을 설명하였다. Tri - state pin이나 내부 신호는 없다.

| Туре | Description           |  |  |  |  |  |  |

|------|-----------------------|--|--|--|--|--|--|

| I    | 입력                    |  |  |  |  |  |  |

| 0    | 8mA 출력 driving 전류     |  |  |  |  |  |  |

| 10   | 입/출력 (Bidirectional)  |  |  |  |  |  |  |

| Pu   | 4.7KΩ저항 내부 pulled-up  |  |  |  |  |  |  |

| Pd   | 85KΩ저항 내부 pulled-down |  |  |  |  |  |  |

## 1.4.2.1 Configuration

| Pin name | Pin nu | mber  | 1/0 | Pu/Pd | Desc | ript  | ion   |                               |

|----------|--------|-------|-----|-------|------|-------|-------|-------------------------------|

|          | 100pin | 64pin |     |       |      |       |       |                               |

| nRST     | 8      | 9     | ı   | Pu    | Glob | oal a | syn   | chronous reset, Active low    |

| TM3-0    | 1,2,   | 2,3,  | I   | Pd    | Must | t be  | con   | nected to GND; value '0000'   |

|          | 3,4    | 4,5   |     |       |      |       |       |                               |

| PM2 - 0  | 70,    | -     | I   | Pd    | PHY  | Мос   | de    |                               |

|          | 71,    |       |     |       |      | РМ    |       | Donasistics.                  |

|          | 72     |       |     |       | 2    | 1     | 0     | Description                   |

|          |        |       |     |       | 0    | _     | 0     | Normal Operation Mode, 모든 기능  |

|          |        |       |     |       |      | 0     | U     | 과 Auto-negotiation기능 활성화      |

|          |        |       |     |       | 0    | 0     | 1     | 100 BASE-TX FDX/HDX 기능과 Auto- |

|          |        |       |     |       |      | U     | ľ     | negotiation기능 활성화             |

|          |        |       |     |       | 0    | 1     | 0     | 10 BASE-T FDX/HDX 기능과 Auto-   |

|          |        |       |     |       |      | ı     | U     | negotiation 기능 활성화            |

|          |        |       |     |       | 0    | 1     | 1     | Reserved                      |

|          |        |       |     |       | 1    | 0     | 0     | 100 BASE-TX FDX 직접 선택         |

|          |        |       |     |       | 1    | 0     | 1     | 100 BASE-TX HDX 직접 선택         |

|          |        |       |     |       | 1    | 1     | 0     | 10 BASE-T FDX 직접 선택           |

|          |        |       |     |       | 1    | 1     | 1     | 10 BASE-T HDX 직접 선택           |

|          |        |       |     |       | FDX  | : Fu  | ıll-D | uplex, HDX : Half-Duplex      |

| BOOTEN   | 5      | 6     | I   | Pd    | Boot | t En  | able  | e/Disable                     |

|          |        |       |     |       | 0 -  | 사용    | 자     | Application 실행                |

|          |        |       |     |       | Co   | de F  | LAS   | SH 의 시작주소 0x0000로 jump        |

|          |        |       |     |       | 1- E | nabl  | e Bo  | pot                           |

|          |        |       |     |       | Вос  | ot R  | OM⊆   | 의 Boot code실행                 |

| PLOCK    | 77     | 51    | 0   | -     | PLL  | Locl  | k lin | e, 내부 PLL의 locked 상태를 알려줌     |

## 1.4.2.2 Timer

|                     | ., .,_,    |       |     |       |                    |  |  |  |

|---------------------|------------|-------|-----|-------|--------------------|--|--|--|

| Pin name            | Pin number |       | 1/0 | Pu/Pd | Description        |  |  |  |

|                     | 100pin     | 64pin |     |       |                    |  |  |  |

| Timer0, 1 Interface |            |       |     |       |                    |  |  |  |

| ТО                  | 9          | -     | I   | Pu    | Timer0 외부 clock 입력 |  |  |  |

| T1                  | 10         | -     | Ι   | Pu    | Timer1 외부 clock 입력 |  |  |  |

| GATE0               | 11         | -     | I   | Pd    | Timer0 gate 컨트롤    |  |  |  |

| GATE1               | 12         | -     | _   | Pd    | Timer1 gate 컨트롤    |  |  |  |

| Timer2 Interface |    |   |   |    |                               |  |  |

|------------------|----|---|---|----|-------------------------------|--|--|

| T2               | 13 | - | I | Pu | Timer2 외부 clock 입력            |  |  |

| T2EX             | 14 | - | I | Pu | Timer2 Capture/Reload trigger |  |  |

## 1.4.2.3 UART

| Pin name | Pin number |       | 1/0 | Pu/Pd | Description  |

|----------|------------|-------|-----|-------|--------------|

|          | 100pin     | 64pin |     |       |              |

| RXD      | 15         | 10    | - 1 | -     | Serial 수신 입력 |

| TXD      | 17         | 12    | 0   | -     | Serial 송신 출력 |

## 1.4.2.4 DoCD™ Compatible Debugger

| Pin name | Pin number |       | 1/0 | Pu/Pd | Description |

|----------|------------|-------|-----|-------|-------------|

|          | 100pin     | 64pin |     |       |             |

| DCDCLK   | 18         | 13    | 0   | -     | DoCD clock  |

| DCDDI    | 19         | 14    | I   | Pu    | DoCD 데이터 입력 |

| DCDDO    | 20         | 15    | 0   |       | DoCD 데이터 출력 |

## 1.4.2.5 Interrupt / Clock

| Pin name | Pin nu |       | 1/0 | Pu/Pd | Description                                  |

|----------|--------|-------|-----|-------|----------------------------------------------|

|          | 100pin | 64pin |     |       |                                              |

| nINT0    | 22     | 17    | I   | -     | 외부 interrupt0                                |

| nINT1    | 23     | -     | I   | Pu    | 외부 interrupt1                                |

| nINT2    | 24     | -     | I   | Pu    | 외부 interrupt2                                |

| nINT3    | 25     | 1     | I   | Pu    | 외부 interrupt3                                |

| XTLN0    | 61     | 40    | 0   | -     | WIZnet Core용 clock output, 25MHz Crystal 혹은  |

|          |        |       |     |       | Ceramic resonator 병렬연결, Oscillator를 사용할      |

|          |        |       |     |       | 경우 floating 함                                |

| XTLP0    | 62     | 41    | I   | -     | WIZnet Core용 clock input, 25MHz Crystal 혹은   |

|          |        |       |     |       | Ceramic resonator와 병렬연결, Oscillator를 사용      |

|          |        |       |     |       | 할 경우 1.8V OSC의 output과 연결함                   |

| XTLN1    | 67     | 45    | 0   | -     | MCU Core용 clock output, 11.0592MHz Crystal 혹 |

|          |        |       |     |       | 은 Ceramic resonator와 병렬연결, Oscillator를       |

|          |        |       |     |       | 사용할 경우 floating 함                            |

| XTLP1    | 66     | 44    | ı   | -     | MCU Core용 clock input, 11.0592MHz Crystal 혹  |

|          |        |       |     |       | 은 Ceramic resonator와 병렬연결, Oscillator를       |

|          |        |       |     |       | 사용할 경우 1.8V OSC의 output과 연결함                 |

## 1.4.2.6 GPIO

| Pin name | Pin nu | mber  | 1/0 | Pu/Pd | Description                     |

|----------|--------|-------|-----|-------|---------------------------------|

|          | 100pin | 64pin |     |       |                                 |

| P0.0     | 81     | 52    | 10  | -     | Port0 입/출력, 외부 메모리 Data0, Addr0 |

| P0.1     | 82     | 53    | 10  | -     | Port0 입/출력, 외부 메모리 Data1, Addr1 |

| P0.2     | 84     | 55    | 10  | -     | Port0 입/출력, 외부 메모리 Data2, Addr2 |

| P0.3     | 85     | 56    | 10  | -     | Port0 입/출력, 외부 메모리 Data3, Addr3 |

| P0.4     | 86     | 57    | 10  | -     | Port0 입/출력, 외부 메모리 Data4, Addr4 |

| P0.5     | 88     | 59    | 10  | -     | Port0 입/출력, 외부 메모리 Data5, Addr5 |

| P0.6     | 89     | 60    | 10  | -     | Port0 입/출력, 외부 메모리 Data6, Addr6 |

| P0.7     | 90     | 61    | 10  | -     | Port0 입/출력, 외부 메모리 Data7, Addr7 |

| P1.0     | 26     | 18    | 10  | -     | Port1 입/출력, 외부 메모리 Addr0        |

| P1.1     | 27     | 19    | 10  | -     | Port1 입/출력, 외부 메모리 Addr1        |

| P1.2     | 28     | 20    | 10  | -     | Port1 입/출력, 외부 메모리 Addr2        |

| P1.3     | 29     | 21    | 10  | -     | Port1 입/출력, 외부 메모리 Addr3        |

| P1.4     | 30     | 22    | 10  | -     | Port1 입/출력, 외부 메모리 Addr4        |

| P1.5     | 31     | 23    | 10  | -     | Port1 입/출력, 외부 메모리 Addr5        |

| P1.6     | 32     | 24    | 10  | -     | Port1 입/출력, 외부 메모리 Addr6        |

| P1.7     | 33     | 25    | 10  | -     | Port1 입/출력, 외부 메모리 Addr7        |

| P2.0     | 91     | 62    | 10  | -     | Port2 입/출력, 외부 메모리 Addr8        |

| P2.1     | 93     | 64    | 10  | -     | Port2 입/출력, 외부 메모리 Addr9        |

| P2.2     | 94     | 1     | 10  | -     | Port2 입/출력, 외부 메모리 Addr10       |

| P2.3     | 95     | 1     | 10  | -     | Port2 입/출력, 외부 메모리 Addr11       |

| P2.4     | 96     | ı     | 10  | -     | Port2 입/출력, 외부 메모리 Addr12       |

| P2.5     | 97     | ı     | 10  | -     | Port2 입/출력, 외부 메모리 Addr13       |

| P2.6     | 98     | ı     | 10  | -     | Port2 입/출력, 외부 메모리 Addr14       |

| P2.7     | 99     | -     | 10  | -     | Port2 입/출력, 외부 메모리 Addr15       |

| P3.0     | 34     | ı     | 10  | -     | Port3 입/출력, 외부 메모리 Addr16       |

| P3.1     | 35     | -     | 10  | -     | Port3 입/출력, 외부 메모리 Addr17       |

| P3.2     | 37     | -     | 10  | -     | Port3 입/출력, 외부 메모리 Addr18       |

| P3.3     | 39     | -     | 10  | -     | Port3 입/출력, 외부 메모리 Addr19       |

| P3.4     | 40     | -     | 10  | -     | Port3 입/출력, 외부 메모리 Addr20       |

| P3.5     | 41     | -     | Ю   | -     | Port3 입/출력, 외부 메모리 Addr21       |

| P3.6     | 42     | -     | 10  | -     | Port3 입/출력, 외부 메모리 Addr22       |

| P3.7     | 43     | -     | 10  | -     | Port3 입/출력, 외부 메모리 Addr23       |

주의: GPIO의 입/출력 driving 전압은 Px\_PU/Px\_PD SFR을 설정하여 제어한다.

참고: 외부 메모리를 사용하는 경우, GPIOO-3은 외부 메모리 주소와 데이터 전송에 이용됨.

자세한 사항은 '2.3 External Data Memory Access' 참고.

## 1.4.2.7 External Memory Interface

| Pin name | Num | I/O Type | Description                                |

|----------|-----|----------|--------------------------------------------|

| ALE      | 78  | 0        | Data memory address bus [7:0] latch enable |

| nWR      | 79  | OL       | External data memory write                 |

| nRD      | 80  | OL       | External data memory read                  |

참고 : 외부 메모리를 Standard 8051 Interface로 사용 시, ALE pin을 제어하여 P0[7:0]을 Data와 Address로 번갈아 사용

#### 1.4.2.8 Media Interface

| Pin name | Pin number |       | 1/0 | Pu/Pd | Description                           |

|----------|------------|-------|-----|-------|---------------------------------------|

|          | 100pin     | 64pin |     |       |                                       |

| TXON     | 52         | 32    | 0   | -     | TXON/TXOP 신호 쌍, 전송 시에 differential 데  |

| TXOP     | 53         | 33    | 0   | -     | 이터는 TXON/TXOP 신호 쌍을 통해 전송됨            |

| RXIN     | 55         | 35    | I   | -     | RXIN/RXIP 신호 쌍, 수신 시에 differential 데이 |

| RXIP     | 56         | 36    | I   | -     | 터는 RXIN/RXIP 신호 쌍을 통해 수신됨             |

| RESETBG  | 59         | 38    | I   | -     | PHY Off-chip 저항, 12.3㎞±1% 저항을 통해 그라   |

|          |            |       |     |       | 운드에 연결됨, 'Reference schematic'을 참고    |

최상의 성능을 위해서는,

- 1. RXIP/RXIN 신호 쌍 (RX) 을 가능한 같은 길이로 만듦.

- 2. TXOP/TXON 신호 쌍 (TX) 을 가능한 같은 길이로 만듦.

- 3. RXIP와 RXIN 신호를 가능한 가깝게 위치시킴.

- 4. TXIP와 TXIN 신호를 가능한 가깝게 위치시킴.

- 5. RX와 TX 신호 쌍은 noisy 신호와 멀리 위치시킴.

- 6. TX/RX 신호 쌍의 간격을 일정하게 유지함.

자세한 사항은 'W5100 Layout Guide.pdf'를 참고.

#### 1.4.2.9 Network Indicator LED

| Pin name | Pin number |       | 1/0 | Pu/Pd | Description       |

|----------|------------|-------|-----|-------|-------------------|

|          | 100pin     | 64pin |     |       |                   |

| SPDLED   | 45         | 27    | 0   | -     | Link speed LED    |

|          |            |       |     |       | Low: 100Mbps      |

|          |            |       |     |       | High: 10Mbps      |

| FDXLED   | 46         | -     | 0   | -     | Full duplex LED   |

|          |            |       |     |       | Low: Full-duplex  |

|          |            |       |     |       | High: Half-duplex |

| COLLED  | 47 | -  | 0 | - | Collision LED                              |

|---------|----|----|---|---|--------------------------------------------|

|         |    |    |   |   | Low: Collision detected (only half-duplex) |

| RXLED   | 48 | -  | 0 | - | Receive activity LED                       |

|         |    |    |   |   | Low: Receive signal detected on RXIP/RXIN  |

| TXLED   | 49 | -  | 0 | - | Transmit activity LED                      |

|         |    |    |   |   | Low: Transmit signal detected on TXOP/TXON |

| LINKLED | 50 | 28 | 0 | - | Link LED                                   |

|         |    |    |   |   | Low: Link (10/100M) is detected            |

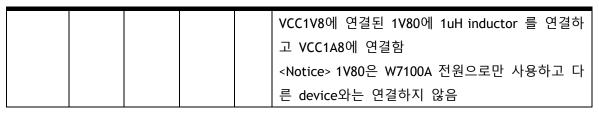

## 1.4.2.10 Power Supply Signal

| 1.7.2.1 |        |        | uppty - | .5  |                                          |

|---------|--------|--------|---------|-----|------------------------------------------|

| Pin     | Pin nu | ımber  | 1/0     | Pu/ | Description                              |

| name    | 100pin | 64pin  |         | Pd  |                                          |

| VCC3A3  | 58, 75 | 37, 49 | Power   | -   | Analog 3.3V power supply                 |

|         |        |        |         |     | 안정적인 전원 공급을 위해 VCC3A3 과 GNDA사            |

|         |        |        |         |     | 이에 10uF tantalum capacitor를 연결           |

| VCC3V3  | 21,38, | 16, 58 | Power   | -   | Digital 3.3V power supply                |

|         | 73,87, |        |         |     | 각 VCC와 GND쌍에는 0.1uF decoupling capacitor |

|         | 100    |        |         |     | 를 연결, 1uH ferrite bead는 VCC3V3과 VCC3A3을  |

|         |        |        |         |     | 구분하는데 사용                                 |

| VCC1A8  | 54,60, | 34, 42 | Power   | -   | Analog 1.8V power supply                 |

|         | 64     |        |         |     |                                          |

| VCC1V8  | 16,44, | 39,46, | Power   | -   | Digital 1.8V power supply                |

|         | 68, 83 | 54, 11 |         |     | 각 VCC와 GND쌍에는 0.1uF decoupling capacitor |

|         |        |        |         |     | 를 연결                                     |

| GNDA    | 51,57, | 31,    | Power   | -   | Analog ground                            |

|         | 63,65, | 43, 50 |         |     | PCB 레이아웃에 analog ground 면적은 가능한 크        |

|         | 76     |        |         |     | 게 디자인 하는 것이 좋음                           |

| GND     | 6, 7,  | 7, 8,  | Power   | -   | Digital ground                           |

|         | 36,    | 26,    |         |     | PCB 레이아웃에 digital ground 면적은 가능한 크       |

|         | 69, 92 | 47, 63 |         |     | 게 디자인 하는 것이 좋음                           |

| 1V8O    | 74     | 48     | Power   | -   | 1.8V regulated output voltage            |

|         |        |        |         |     | Core operation 전원과 내부 regulator에 의해      |

|         |        |        |         |     | 1.8V/150mA 전원을 만듦 (VCC1A8, VCC1V8)       |

|         |        |        |         |     | 출력 주파수를 안정시키기 위해 1V8O과 GND사이             |

|         |        |        |         |     | 에 3.3uF tantalum capacitor를 연결하고 고주파     |

|         |        |        |         |     | noise decoupling을 위해 0.1uF capacitor를 연결 |

|         |        |        |         |     | 함                                        |

Figure 1.9 Power Design

## 1.5 64pin package description

### 1.5.1 Difference between 100 and 64pin package

|                  |                                               | <u> </u>            |  |  |

|------------------|-----------------------------------------------|---------------------|--|--|

| Difference       | 64 pin                                        | 100 pin             |  |  |

|                  | T0, T1, GATE0, GATE1, T2, T2EX, nINT1, nINT2, |                     |  |  |

| Deleted pin      | nINT3, FDXLED, COLLED, RXLED, TXLED, PM2,     |                     |  |  |

|                  | PM1, PM0, EXTALE, EXTDATAWR, EXTDATARD,       | <del>-</del>        |  |  |

|                  | GPIO3[0:7], GPIO2[3:7]                        |                     |  |  |

| External memory  | X                                             | 0                   |  |  |

| PHY mode setting | only use SFR                                  | use SFR and PM pins |  |  |

| GPIO             | max 19pin                                     | max 32pin           |  |  |

\*Note: 64pin package의 경우 PHY모드를 SFR을 이용해서 설정해야만 한다. 그러므로 칩 초기화 시 PHYCONF SFR의 MODE\_EN bit를 설정해서 MODE2~0 bit를 이용해서 PHY mode를 설정할 수 있도록 한다. 그 다음 MODE2~0의 값을 설정하고 PHY\_RSTn bit를 이용해서 PHY를 reset해야만 칩이 초기화되어 정상동작 한다. 그러므로 64pin package칩을 사용할 때는 반드시 아래 코드가 초기화 루틴에 포함되어 있어야만 한다.

PHYCONF SFR에 대한 자세한 내용은 section 2.5.10 'New & Extended SFR' 을 참조하기 바라다.

```

PHYCONF |= 0x08; // MODE_EN bit enable

```

PHYCONF &= 0xF8; // MODE2 ~ 0 value is 0 (normal mode)

PHYCONF |= 0x20; // Set the PHY\_RSTn bit (reset bit)

Delay(); // Delay for reset timing (refer to the section 10 'Reset Timing')

PHYCONF &= ~(0x20); // Clear the PHY\_RSTn bit

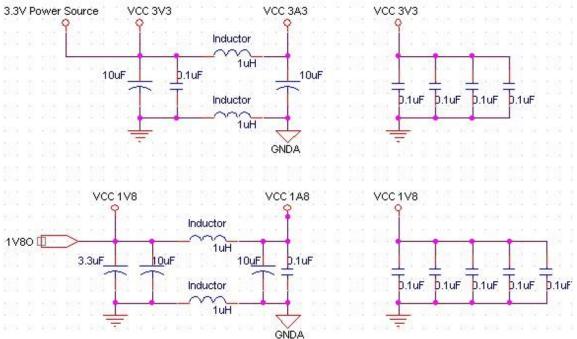

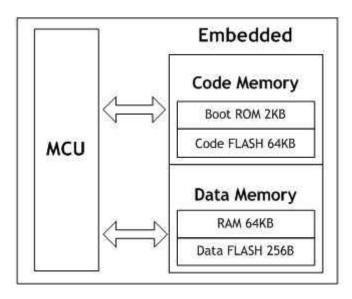

## 2 Memory

W7100A의 메모리는 'Code Memory'와 'Data Memory'의 두 가지 타입으로 나뉜다. Code, Data memory별로 각각 memory lock을 설정할 수 있다. Lock기능을 설정하면 외부에서 메모리를 read하는 것을 방지할 수 있다. Memory lock이 설정되면 W7100A Debugger를 사용할수 없기 때문에 주의해야 한다. Lock기능 사용에 대한 보다 자세한 내용은 "WizISP Program Guide"문서를 참조하기 바란다. W7100A의 Memory 구성을 Figure 2.1에 간략히 나타내었다.

Figure 2.1 Code / Data Memory Connections

#### \*Note:

전원 공급 장치의 전압이 충분치 않은 동안의 시스템 오작동을 방지하기 위하여 외부 전원 공급 장치의 저전압 검출기(Low Voltage Detector) 사용을 권장하며, 이를 통해 비휘발성 메 모리(Non-volatile Memory)와 SRAM, CPU의 손상을 예방할 수 있다. <u>WIZnet 웹사이트</u>의 iMCU7100EVB Schematic을 참조하기 바란다.

(Example ICs: MAX811, MIC811, DS1811)

## 2.1 Code Memory

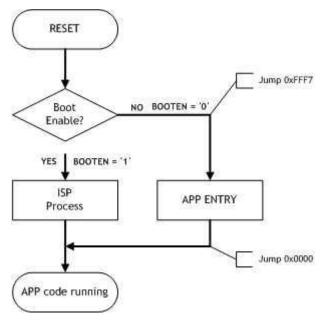

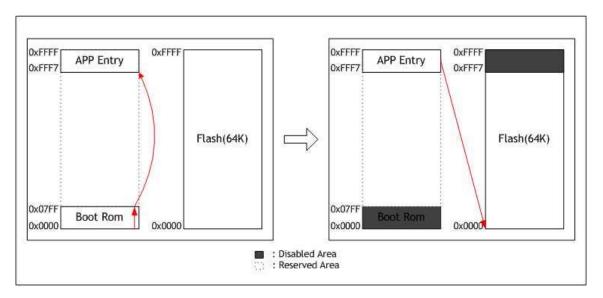

'Code Memory'는 0x0000부터 0x07FF까지의 주소를 갖는 Boot ROM과 0x0000부터 0xFFFF까지의 주소를 갖는 Code FLASH로 구성된다. 시스템이 reset된 다음 Boot ROM의 code가 실행되는데 이 때 BOOTEN핀에 따라 동작이 달라진다. Figure 2.2는 시스템부팅 후에 BOOTEN핀에 따른 BootROM코드의 flow를 나타내고 있다. BOOTEN = 1인 경우 ISP 프로세스가 실행되고, BOOTEN = 0인 경우 APP Entry와 사용자 Application코드가 실행된다. ISP 프로세스는 WizISP program을 이용해서 W7100A에 사용자 code를 write할 때 사용한다. 그리고 APP Entry는 사용자 Application code가 실행될 수 있도록 memory map switching이 일어날 수 있도록 한다. 초기 상태에서 W7100A는 아래 Figure 2.3에서와 같이 Boot ROM, APP Entry 그리고 FLASH영역의 세가지 메모리 영역을 갖는다. 하지만 그림에서 알 수 있듯이, Boot ROM과 APP Entry는 FLASH영역과 검친다. 그래서 W7100A는 초기화 시 Boot ROM과 APP Entry영역은 code메 모리로 FLASH영역은 data메모리로 설정된다.

Figure 2.2. Boot Sequence Flowchart

FLASH영역을 data memory로 설정했기 때문에 사용자 application code를 FLASH에 write할수 있다. 하지만 이 상태에서는 FLASH를 code메모리로 사용할 수 없다. FLASH를 코드메모리로 사용하기 위해서는 memory map switching이 필요하다. 이 때문에 사용자는 부팅 시BOOTEN = 0으로 선택하여 APP모드를 선택한다. 그러면 Boot ROM 코드는 APP Entry로 즉시 jump한다. 그 후 APP Entry는 Boot ROM을 un-map하고 FLASH를 map시켜서 Code FLASH로 사용할 수 있도록 한다. code memory map switching이 끝나면 APP Entry는 Code FLASH의 시작 주소인 0x0000으로 jump한다. 이 과정은 Figure 2.3에 나타내었다.

Figure 2.3 APP Entry Process

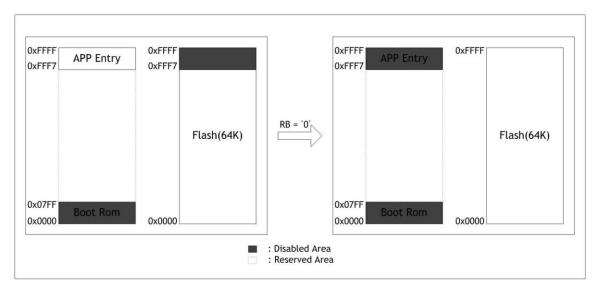

하지만 여전히 FLASH와 APP Entry는 서로 겹치는 address영역을 가지므로, FLASH 64KB를 전부 사용하기 위해서는 APP Entry를 un-map해야 한다. 이를 위해 startup code에서 WCONF(0xFF)의 RB비트를 '0'으로 설정해줘야 한다. 그러면 Figure 2.4와 같이 APP Entry는 un-map된다.

Figure 2.4 Changing the code memory Status at RB = '0'

# WCONF (0xFF)

| 7  | 6     | 5   | 4   | 3   | 2        | 1  | 0  | Reset |

|----|-------|-----|-----|-----|----------|----|----|-------|

| RB | ISPEN | EM2 | EM1 | EM0 | RESERVED | FB | BE | 0x00  |

Code FLASH가 0xFFF7이상의 주소를 가지게 된다면, 반드시 아래 코드를 startup code에 삽입해야 한다. 이 방법을 이용하면, W7100A는 system reset후에 즉시 APP Entry address를 disable할 것이다.

ANL 0FFH, #07FH ; Clear Reboot flag

BOOTEN핀을 '0'으로 설정하고 Startup code에서 WCONF register의 RB비트를 clear하면 내부 Code FLASH memory 64KB를 모두 code memory로 사용할 수 있다.

#### 2.1.1 Code Memory Wait States

Code memory wait state는 내부 WTST (0x92) register에 의해 설정되고 wait state의 종류도 WTST register의 값에 의해 결정된다. 자세한 내용은 section 2.5.10 'New & Extended SFR'을 참고하기 바란다.

## 2.2 Data Memory

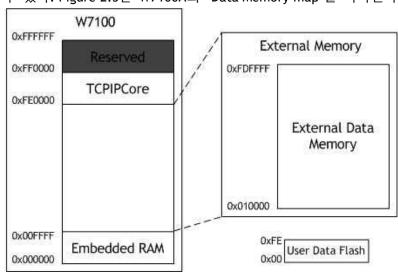

W7100A는 내부에 64KB RAM, 64KB TCPIPCore, 255Byte Data FLASH를 포함하고 있다. Data FLASH는 사용자의 IP, MAC, subnet mask, port번호 등을 저장하는데 사용할 수 있다. 또 한 W7100A는 외부메모리를 최대 16Mbyte까지 확장할 수 있다. 이 memory들은 MOVX 명령으로만 access할 수 있다. Figure 2.5는 W7100A의 'Data Memory map'을 나타낸다.

Figure 2.5 "Data Memory" Map

## 2.2.1 Data Memory Wait States

Data memory wait state는 CKCON (0x8E) register에 의해 설정된다. CKCON register에 설정된 값에 따라 wait state 수가 결정된다. section 2.5.10 'New & Extended SFR'을 참조하기 바란다.

## 2.3 External Data Memory Access

외부 메모리를 사용할 때, 외부 address, data 핀의 access mode는 크게 2가지 방법이 있다. 첫 번째는 standard 8051에서 사용하는 방법으로 address line에 latch를 사용하는 방법이고, 두 번째는 address line에 direct로 모든 라인을 연결하는 방법이다. 물론 address와 data 핀은 모두 GPIO(General Purpose I/O)의 용도로 사용이 가능하다. 외부메모리 accessing speed 에 대한 정보는 section 10 'Electrical specification'을 참조하기 바란다.

아래 테이블에 EM[2:0]설정에 따른 external data memory access mode들을 정리하였다.

| Mode       | EM[2:0] | P0[7:0]             | P1[7:0]   | P2[7:0]    | P3[7:0]     |

|------------|---------|---------------------|-----------|------------|-------------|

| Standard 1 | 001     | Addr[7:0]/Data[7:0] | GPIO      | Addr[15:8] | GPIO        |

| Standard 2 | 011     | Addr[7:0]/Data[7:0] | GPIO      | Addr[15:8] | Addr[23:16] |

| Direct 1   | 101     | Data[7:0]           | Addr[7:0] | Addr[15:8] | GPIO        |

| Direct 2   | 111     | Data[7:0]           | Addr[7:0] | Addr[15:8] | Addr[23:16] |

Table 2.1 External memory access mode

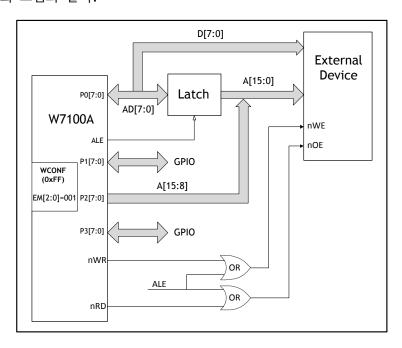

#### 2.3.1 Standard 8051 Interface

이 방법은 일반적인 8051의 외부 인터페이스와 동일하다. Port0의 address와 data신호를 구분하기 위해 ALE (Address Latch Enable) pin을 이용하여 latch enable 신호를 제어한다. ALE신호가 유지되는 시간은 ALECON register를 통해 제어할 수 있으며, 보다 자세한 내용은 section 2.5.10 'New & Extended SFR'을 참조하기 바란다.

SFR register인 WCONF(0xFF)에 위치한 EM[2:0](External Memory Mode)의 setting에 따라 접근할 수 있는 address의 범위가 두 가지로 나뉜다. 먼저 EM[2:0]을 "001"로 setting하게 되면 port0을 address/data bus로 사용하고, port2를 상위 address(addr[15:8])로 사용하므로 총 16-bit address를 사용하게 된다. Address/data line으로 사용되지 않는 port1, port3은 GPIO로 사용된다.

#### Note:

Standard 8051 interface를 이용한 외부 메모리 인터페이스는 WR / RD 신호 enable 전에 ALE 신호가 발생되어야 하나, 현재 WR/RD 신호가 enable 된 이후에 ALE 신호가 발생하는 Erratum이 있다. 때문에 WR/RD를 ALE와 OR하여 외부 메모리의 nWR, nOE로 연결하면 문제가 해결된다. 더 자세한 내용은 'W7100A Errata sheet - Erratum3'을 참조하라

구성은 아래의 그림과 같다.

Figure 2.6 Standard 8051 External Pin Access Mode (EM[2:0] = "001")

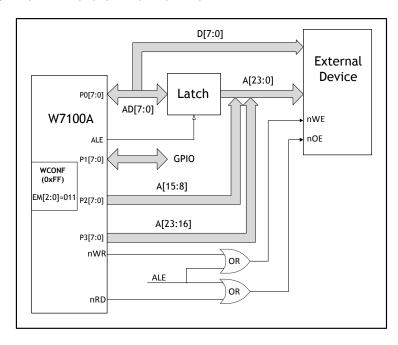

다음으로 EM[2:0]을 "011"로 설정하게 되면 port0은 address/data bus로 사용하게 되고, port2는 상위 address(addr[15:0])로 사용된다. 그리고 port3을 최상위 address(addr[23:16])로 사용할 수 있어 address의 범위가 24-bit로 늘어난다. 마지막으로 port1은 GPIO로 사용이가능하다. 자세한 구성은 아래의 블록도와 같다.

Figure 2.7 Standard 8051 External Pin Access Mode (EM[2:0] = "011")

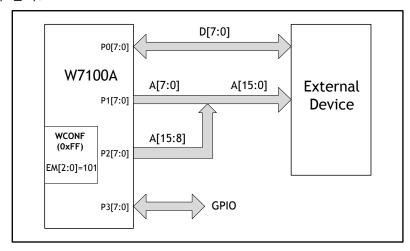

#### 2.3.2 Direct Interface

이 방법은 standard 8051의 외부 연결 방법과는 다르게 address와 data 라인을 직접 연결하여 사용하는 것이다. 먼저 EM[2:0]을 "101"로 setting하게 되면, port0을 data line (data[7:0])으로 사용하게 되며, port1을 하위 address(addr[7:0])으로 사용하고, port2를 상위 address(addr[15:8])로 사용하게 된다. 그리고 남아있는 port3은 GPIO로 사용이 가능하다. 이 방법을 사용하게 되면 latch 없이 address/data 라인의 연결이 가능하다. 자세한 구성은 아래의 블록도와 같다.

Figure 2.8 Direct 8051 External Pin Access Mode (EM[2:0] = "101")

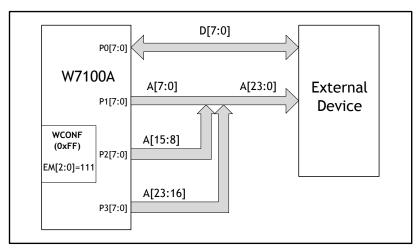

다음으로 EM[2:0]을 "111"로 setting하게 되면, port0, port1, port2의 구성은 위의 구성과 같고, port3을 최상위 address(addr[23:16])로 사용할 수 있다. 자세한 구성은 아래의 블록도와 같다.

Figure 2.9 Direct 8051 External Pin Access Mode (EM[2:0] = "111")

## 2.4 Internal Data Memory and SFR

아래 그림은 내부 memory와 Special Function Register (SFR) map을 보여준다.

| 0xFF<br>0x80 | Upper Internal RAM shared with Stack space (indirect addressing) | SFR<br>Special Function Registers<br>(direct addressing) |

|--------------|------------------------------------------------------------------|----------------------------------------------------------|

| 0x7F<br>0x30 |                                                                  | hared with Stack space<br>ect addressing)                |

| 0x2F<br>0x20 | bit addres                                                       | esable area                                              |

| 0x1F<br>0x00 | 4 banks, R                                                       | 0-R7 each                                                |

Figure 2.10 Internal Memory Map

W7100A의 내부 RAM은 0x00 ~ 0x1F까지 8개의 register들로 구성된 4개의 register bank들을 포함하고 있고, 0x20부터 128bits (16bytes)의 bit-addressable 부분과 208bytes의 scratchpad 부분으로 구성되어 있다. Indirect addressing mode로 0x80부터 0xFF까지 addressing하면, 최 상위부터 128 Bytes 는 내부 memory로 accessing된다. 하지만 direct addressing mode로 0x80부터 0xFF까지 addressing하면 이 부분은 SFR memory로 accessing된다.

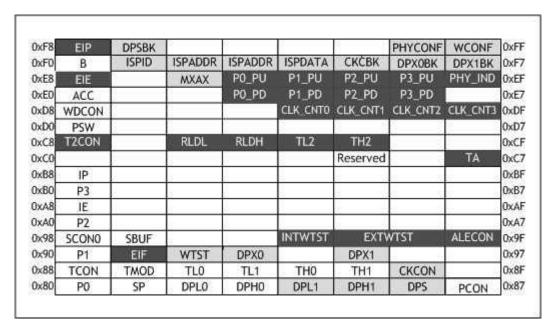

Figure 2.11 SFR Memory Map

New SFR - New additional SFR

Extended SFR - Standard 8051에서 확장된 SFR

Standard - Standard 8051 SFR

Figure 2.11의 표에서 왼쪽 행 0혹은 8로 끝나는 SFR은 bit addressable register이다.

#### 2.5 SFR definition

이 section에서는 W7100A의 SFR과 그 기능들에 대해 설명한다. 더 자세한 사항은 section 2.5.11 'Peripheral SFR'을 참고하기 바란다.

## 2.5.1 Program Code Memory Write Enable Bit

PCON register 내부에 Program Write Enable (PWE) bit는 MOVX 명령이 수행되는 동안 Program Write signal을 제어한다. PWE bit를 '1'로 설정하면 'MOVX @DPTR, A' 명령은 accumulator register의 데이터를 DPTR (active DPH:DPL) register를 통해 설정된 code memory address에 write한다.

'MOVX @Rx, A' 명령은 accumulator register의 데이터를 P2 (bits 15:8) register와 RX(bits 7:0) register를 통해 설정된 code memory address에 write한다.

#### PCON (0x87)

| 7     | 6 | 5 | 4   | 3 | 2 | 1 | 0 | Reset |

|-------|---|---|-----|---|---|---|---|-------|

| SMOD0 | - | - | PWE | - | 0 | 0 | 0 | 0x00  |

Figure 2.12 PWE bit of PCON Register

Note: 1. PCON.2 ~ PCON.0 bit는 reserved이며 반드시 0으로 설정해야 한다.

#### 2.5.2 Program Code Memory Wait States Register

Wait state register는 code memory access time을 설정하는데 쓰인다.

WTST (0x92)

| 7 | 6 | 5 | 4 | 3 | 2      | 1      | 0      | Reset |

|---|---|---|---|---|--------|--------|--------|-------|

| - | - | - | - | - | WTST.2 | WTST.1 | WTST.0 | 0x07  |

Figure 2.13 Code memory Wait States Register

Note: 1. 위 bit들은 오직 program fetch나 MOVC명령에 영향을 준다.

Code memory write는 MOVX명령에 의해 수행되므로, CKCON register는 CODE-W R pulse width를 제어한다.

2. Read cycle은 최소 4 clock에서 최대 8 clock까지 주기를 갖는다.

Table 2.2 WTST Register Values

| Access Time [clk] |

|-------------------|

| 8                 |

| 7                 |

| 6                 |

| 5                 |

| Not Used          |

| Not Used          |

| Not Used          |

| Not Used          |

|                   |

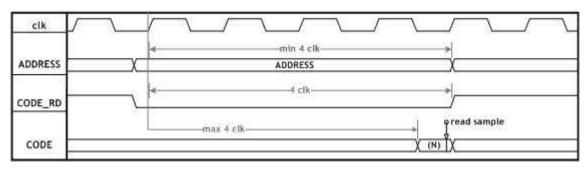

명령어 fetching을 수행하는 도중에는, code memory는 오직 MOVC명령에 의해서만 access될 수 있다. Code memory는 최소 4 wait states로 read할 수 있다. 그 Timing 다이어그램을 아래 그림에 나타내었다.

Figure 2.14 Waveform for code memory Synchronous Read Cycle with Minimal Wait States (WTST = '4')

Note: 1. clk - 시스템 clock 주파수(88.4736 MHz)

- 2. ADDRESS -실제 수정된 program byte 의 주소

- 3. CODE\_RD Code memory의 read신호

- 4. CODE Data write to the actual modified program byte

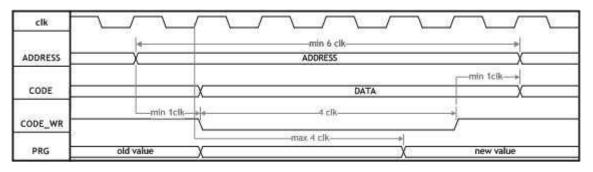

Code memory는 최소 4 wait states의 MOVX명령으로 write할 수 있다. W7100A core는 wait state를 통해 고속과 저속 memory모두에서 잘 동작할 수 있다. 아래그림은 Timing diagram 을 보여준다.

Figure 2.15 Waveform for code memory Synchronous Write Cycle with Minimal Wait State s(WTST = '4')

Note: 1. clk - 시스템 clock 주파수 (88.4736 MHz)

- 2. ADDRESS 실제 수정된 program byte 의 주소

- 3. CODE Data write to the actual modified program byte

- 4. CODE\_WR Code memory의 write신호

- 5. PRG Code memory 상태

## 2.5.3 Data Pointer Extended Registers

Data pointer extended register DPX0, DPX1, MXAX는 64KB이상의 데이터를 accessing할 때 최상위 memory address값을 갖는다. Reset후 DPX0, DPX1, MXAX는 초기값으로 0x00을 갖는다.

|        |       |       |       | 170 (0773 | ')    |       |       |       |

|--------|-------|-------|-------|-----------|-------|-------|-------|-------|

| 7      | 6     | 5     | 4     | 3         | 2     | 1     | 0     | Reset |

| DPXP.7 | DPX.6 | DPX.5 | DPX.4 | DPX.3     | DPX.2 | DPX.1 | DPX.0 | 0x00  |

DPX0 (0x93)

Figure 2.16 Data Pointer Extended Register

|        |        |        | D      | PX1 (0x95 | )      |        |        |       |

|--------|--------|--------|--------|-----------|--------|--------|--------|-------|

| 7      | 6      | 5      | 4      | 3         | 2      | 1      | 0      | Reset |

| DPX1.7 | DPX1.6 | DPX1.5 | DPX1.4 | DPX1.3    | DPX1.2 | DPX1.1 | DPX1.0 | 0x00  |

Figure 2.17 Data Pointer Extended Register

|        |        |        | W      | XAX (0xEA | .)     |        |        |       |

|--------|--------|--------|--------|-----------|--------|--------|--------|-------|

| 7      | 6      | 5      | 4      | 3         | 2      | 1      | 0      | Reset |

| MXAM.7 | MXAX.6 | MXAX.5 | MXAX.4 | MXAX.3    | MXAX.2 | MXAX.1 | MXAX.0 | 0x00  |

Figure 2.18 MOVX @RI Extended Register

MOVX명령이 DPTR0/DPTR1 register를 이용해서 수행되면, 최상위 address A[23:16] 는 항상 DPX0(0x93)/DPX1(0x95)에 설정된 값을 갖는다. MOVX명령이 R0혹은 R1 register를 이용해서

수행되면, 최상위 address A[23:16]는 MXAX(0xEA)의 값을 갖고 A[15:8]은 P2(0xA0)의 값을 갖는다.

### 2.5.4 Data Pointer Registers

Dual data pointer register들은 data block copy속도를 향상시키기 위해 만들어졌다. DPTRO와 DPTR1은 4개의 SFR영역에 위치하고 있다. Active DPTR register는 SEL bit (0x86.0)를 통해 선택할 수 있다. 만약 SEL bit가 '0'이면, DPTR0 (0x83:0x82) 가 선택된다. 반대로 SEL bit가 '1'이면 DPTR1 (0x85:0x04)가 선택된다.

DPTR0(0x83:0x82)

| DPH0(0x83) |   |   |   |   |   | DPL0(0x82) |   |   |   |   |   |   | Reset |   |   |        |

|------------|---|---|---|---|---|------------|---|---|---|---|---|---|-------|---|---|--------|

| 7          | 6 | 5 | 4 | 3 | 2 | 1          | 0 | 7 | 6 | 5 | 4 | 3 | 2     | 1 | 0 | 0x0000 |

Figure 2.19 Data Pointer Register DPTR0

#### DPTR1(0x85:0x84)

| DPH1(0x85) |   |   |   |   |   | DPL1(0x84) |   |   |   |   |   | Reset |   |   |   |        |

|------------|---|---|---|---|---|------------|---|---|---|---|---|-------|---|---|---|--------|

| 7          | 6 | 5 | 4 | 3 | 2 | 1          | 0 | 7 | 6 | 5 | 4 | 3     | 2 | 1 | 0 | 0x0000 |

Figure 2.20 Data Pointer 1 Register DPTR1

#### DPS (0x86)

| 7   | 6   | 5   | 4 | 3 | 2 | 1 | 0   | Reset |

|-----|-----|-----|---|---|---|---|-----|-------|

| ID1 | ID0 | TSL | - | - | - | - | SEL | 0x00  |

Figure 2.21 Data Pointer Select Register

**Note:** TSL - Toggle select enable. When TSL is set, this bit toggles the SEL bit by execu ting the following instructions.

INC DPTR

MOV DPTR, #data16

MOVC A, @A + DPTR

MOVX @DPTR, A

MOVX A, @DPTR

When TSL = 0, DPTR related instructions will not affect the state of the SEL bit.

Unimplemented bit - Read as 0 or 1.

Table 2.3 DPTR0, DPTR1 Operations

| ID1 | ID0 | SEL = 0  | SEL = 1   |

|-----|-----|----------|-----------|

| 0   | 0   | INC DPTR | INC DPTR1 |

| 0   | 1   | DEC DPTR | INC DPTR1 |

| 1 | 0 | INC DPTR | DEC DPTR1 |

|---|---|----------|-----------|

| 1 | 1 | DEC DPTR | DEC DPTR1 |

선택된 data pointer register는 다음 명령을 수행하는데 사용한다.

MOVX @DPTR, A

MOVX A, @DPTR

MOVC A, @A + DPTR

JMP @A + DPTR

INC DPTR

MOV DPTR, #data16

#### 2.5.5 Clock Control Register

Clock control register CKCON (0x8E)은 data memory read/write signal pulse width정보를 가지고 있는 MD[2:0] bit를 포함하고 있다.

CKCON (0x8E)

| 7   | 6   | 5 | 4 | 3 | 2   | 1   | 0   | Reset |

|-----|-----|---|---|---|-----|-----|-----|-------|

| WD1 | WD0 | - | - | - | MD2 | MD1 | MD0 | 0x07  |

Figure 2.22 Clock Control Register - STRETCH bits

Data memory read/write signal은 MOVX명령을 수행하는 동안 활성화 된다. MD[2:0] bit는 slow RAM, LCD display와 같은 I/O device들의 통신을 제어하는데 쓰인다. Reset후 MD[2:0] bit 는 0x07의 초기값을 갖는데, 이 값은 느린 device들이 제대로 동작할 수 있는 값이다. 사용자는 MD[2:0] 값을 I/O device의 속도에 따라 그 값을 변경할 수 있다. 또 한 program이 실행 중이라도 상관없이 MD[2:0]의 값을 변경할 수 있다.

Table 2.4 MD[2:0] Bit Values

| MD[2:0] | Pulse Width[clock] |

|---------|--------------------|

| 7       | 8                  |

|         |                    |

| 2       | 3                  |

| 1       | Not Used           |

| 0       | Not Used           |

Read/write pulse width는 최소 3 clock에서 최대 8 clock까지 설정할 수 있다.

# 2.5.6 Internal Memory Wait States Register

Internal Memory Wait States Register INTWTST(0x9C)는 내부에 있는 64KB Ram, TCPIPCore, 255Byte Internal Flash의 access time을 설정하는데 쓰인다.

#### INTWTST (0x9C)

| 7   | 6    | 5   | 4         | 3   | 2 | 1          | 0 | Reset |

|-----|------|-----|-----------|-----|---|------------|---|-------|

| Ram | WTST | TCI | PIPCore W | TST |   | Flash WTST | - | 0xFF  |

Figure 2.23 Internal Memory Wait States Register

- Ram WTST : 내부의 64Kbytes Ram의 access time을 설정하는데 사용되며, 2bit로 구성되어, 0~3의 값으로 설정될 수 있다.

- TCPIPCore WTST : TCPIPCore의 access time을 설정하는데 사용되며, 3bit로 구성되어,

0-7의 값으로 설정될 수 있다.

- Flash WTST: 내부의 64KBytes / 255Bytes Flash의 access time을 설정하는데 사용되며, 3bit로 구성되어, 0-7의 값으로 설정될 수 있다.

Internal ram WTST는 아래의 표와 같이 access time이 설정된다.

Table 2.5 Ram WTST Bit Values

| WTST | Pulse Width[clock] |

|------|--------------------|

| 3    | 5                  |

| 2    | 4                  |

| 1    | 3                  |

| 0    | 2                  |

TCPIPCore, Internal flash WTST는 아래의 표와 같이 access time이 설정된다.

Table 2.6 TCPIPCore / Flash WTST Bit Values

| WTST | Pulse Width[clock] |

|------|--------------------|

| 7    | 10                 |

| 6    | 9                  |

| 5    | 8                  |

| 4    | 7                  |

| 3    | 6                  |

| 2    | 5                  |

| 1    | 4                  |

| 0    | 3                  |

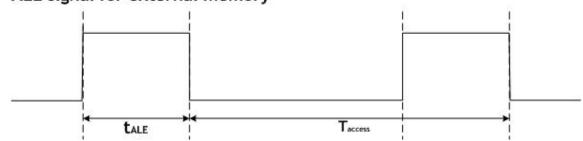

## 2.5.7 Address Latch Enable Register

ALECON이 '0'으로 설정되면, ALE가 1 clock후에 바로 '1'에서 '0'으로 천이된다. ALECON이 'n'으로 설정되면 ALE 신호는 1+n clock을 유지한 다음 '0'으로 천이된다.

ALE maintain duration = ALECON + 1 clock

ALECON의 초기값은 0xFF이다. 따라서 사용자는 외부 장치의 속도에 맞춰 ALECON의 값을 설정 후 사용하면 된다.

|      |      |      | AL   | ECON (0x9 | 9F)  |      |      |       |

|------|------|------|------|-----------|------|------|------|-------|

| 7    | 6    | 5    | 4    | 3         | 2    | 1    | 0    | Reset |

| AC.7 | AC.6 | AC.5 | AC.4 | AC.3      | AC.2 | AC.1 | AC.0 | 0xFF  |

Figure 2.24 Address Latch Enable Control register

## 2.5.8 External Memory Wait States Register

EXTWTST(0x9D, 0x9E)는 외부 메모리 Access속도를 제어하기 위해 사용한다. 총 16bit를 이용해서  $0 \sim 65535$ 까지 값을 설정할 수 있다.

EVTWITCTO (0×0D)

|   | EXTWISIO (0X9D) |      |      |      |      |      |      |      |       |  |  |

|---|-----------------|------|------|------|------|------|------|------|-------|--|--|

|   | 7               | 6    | 5    | 4    | 3    | 2    | 1    | 0    | Reset |  |  |

| _ | EW.7            | EW.6 | EW.5 | EW.4 | EW.3 | EW.2 | EW.1 | EW.0 | 0xFF  |  |  |

Figure 2.25 First Byte of Internal Memory Wait States Register

| EXTWTST1 (0x9E) |       |       |       |       |       |      |      |       |  |  |

|-----------------|-------|-------|-------|-------|-------|------|------|-------|--|--|

| 7               | 6     | 5     | 4     | 3     | 2     | 1    | 0    | Reset |  |  |

| EW.15           | EW.14 | EW.13 | EW.12 | EW.11 | EW.10 | EW.9 | EW.8 | 0xFF  |  |  |

Figure 2.26 Second Byte of Internal Memory Wait States Register

## 2.5.9 Stack Pointer

W7100A는 내부 RAM공간에 8-bit stack pointer SP(0x81)를 가지고 있다.

|      |      |      |      | SP (UX81) |      |      |      |       |

|------|------|------|------|-----------|------|------|------|-------|

| 7    | 6    | 5    | 4    | 3         | 2    | 1    | 0    | Reset |

| SP.7 | SP.6 | SP.5 | SP.4 | SP.3      | SP.2 | SP.1 | SP.0 | 0x07  |

CD (0, 04)

Figure 2.27 Stack Pointer Register

이 pointer는 data가 저장되기 전 PUSH나 CALL명령에 의해 증가하고, 반대로 데이터가 pop되기 전 POP, RET, RETI명령에 의해 감소한다. 즉, stack pointer는 항상 마지막 유효 stack byte를 가리키고 있다.

## 2.5.10 New & Extended SFR

PHY\_IND(0xEF): PHY의 현재 상태를 알려주는 SFR이다.

#### PHY\_IND (0xEF)

| 7 | 6 | 5 | 4 | 3 | 2   | 1   | 0    | Reset |

|---|---|---|---|---|-----|-----|------|-------|

|   |   |   |   |   | FDX | SPD | LINK | 0x00  |

Figure 2.28 PHY Status Register

Note: FDX: 0 - Full duplex / 1 - Half duplex

SPD : 0 - 100Mbps / 1 - 10Mbps

LINK : 0 - The link is down / 1 - The link is up

ISPID(0xF1): ID Register for ISP.

ISPADDR16(0xF2): 16bit Address Register for ISP

ISPDATA(0xF4): Data Register for ISP. CKCBK(0xF5): CKCON Backup Register. DPX0BK(0xF6): DPX0 Backup Register. DPX1BK(0xF7): DPX1 Backup Register. DPSBK(0xF9): DPX Backup Register.

PHYCONF (0xFE): W7100A PHY operation mode, reset, power down configuration register

#### PHYCONF (0xFE)

| 7 | 6 | 5        | 4        | 3       | 2     | 1     | 0     | Reset |

|---|---|----------|----------|---------|-------|-------|-------|-------|

| - | - | PHY_RSTn | PHY_PWDN | MODE_EN | MODE2 | MODE1 | MODE0 | 0x00  |

Figure 2.29 Internal PHY Configuration Register

#### Note:

PHY\_RSTn: W7100A의 내부 Ethernet PHY를 reset한다. 이 bit를 1로 set하고 reset t iming을 참고하여 다시 0으로 clear한다. Reset timing에 대한 보다 자세한 내용은 section 10 'Electrical Specification'을 참조하기 바란다.

PHY\_PWDN: W7100A power down 모드를 설정한다. 1일 때 power down 모드로 동작하고 0일 때 normal모드로 동작한다.

MODE\_EN: 1이면 MODE2 ~ 0 bit를 사용하여 W7100A의 동작 모드를 설정한다. 64pi n package에서는 반드시 이 bit를 설정한 다음 MODE2 ~ 0bit를 설정하여 동작모드를 설정해야만 한다.

MODE2 ~ 0: PHY모드 설정 bit, 설정 값들에 대한 정보는 1.4.2 'Pin Description'의 PM2 ~ 0핀 설정 값과 동일하다.

- : Reserved, must be set to '0'

#### ex> usage of mode selection using MODE2 $\sim 0$

```

PHYCONF |= 0x08; // MODE_EN bit enable

PHYCONF &= 0xF8; // MODE2 ~ 0 value is 0 (normal mode; auto configuration mode)

PHYCONF |= 0x20; // Set the PHY_RSTn bit (reset bit)

```

Delay(); //Delay for reset timing(refer to the section 10 'Electrical Specification')

PHYCONF &= ~(0x20); // Clear the PHY\_RSTn bit

WCONF(0xFF): W7100A configuration register

#### WCONF (0xFF)

| 7  | 6     | 5   | 4   | 3   | 2        | 1  | 0  | Reset |

|----|-------|-----|-----|-----|----------|----|----|-------|

| RB | ISPEN | EM2 | EM1 | EM0 | Reserved | FB | BE | 0x00  |

Figure 2.30 W7100A Configuration Register

Note: RB : 1 - ISP 동작이 끝나면(APP Entry(0xFFF7 ~ 0xFFFF) RD/WR Enable) 재부팅함

0 - ISP동작이 끝나도 재부팅 하지 않음

ISPEN: 0 - ISP enable, 1 - ISP disable

EM[2:0] : 외부 메모리 모드 설정, section 2.3 'External Data Memory Access' 참조

FB : FLASH Busy Flag for ISP. Read only.

BE : Boot Enable (1 - Boot Running / 0 - Apps Running). Read only.

CLKCNTO(0xDC): W7100A core clock count register bit0 ~ 7.

#### CLK\_CNTO (0xDC)

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    | Reset |

|------|------|------|------|------|------|------|------|-------|

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | 0x00  |

Figure 2.31 Core clock count register

Note: CLK\_CNT는 32bit 값으로 매 core clock마다 증가한다. 이 SFR은 core clock을 count 하는데 사용하거나 시간을 재는데 사용할 수 있다.

ex> 1 second = about 88000000 clock count (icore clock is about 88MHz)

CLKCNTO(0xDD): W7100A core clock count register bit8 ~ 15.

#### CLK\_CNT1 (0xDD)

| 7     | 6     | 5     | 4     | 3     | 2     | 1    | 0    | Reset |

|-------|-------|-------|-------|-------|-------|------|------|-------|

| Bit15 | Bit14 | Bit13 | Bit12 | Bit11 | Bit10 | Bit9 | Bit8 | 0x00  |

Figure 2.32 Core clock count register

CLKCNTO(0xDE): W7100A core clock count register bit16 ~ 23.

#### CLK\_CNT2 (0xDE)

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | Reset |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Bit23 | Bit22 | Bit21 | Bit20 | Bit19 | Bit18 | Bit17 | Bit16 | 0x00  |

Figure 2.33 Core clock count register

CLKCNTO(0xDF): W7100A core clock count register bit24 ~ 31.

#### CLK\_CNT3 (0xDF)

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | Reset |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Bit31 | Bit30 | Bit29 | Bit28 | Bit27 | Bit26 | Bit25 | Bit24 | 0x00  |

Figure 2.34 Core clock count register

## 2.5.11 Peripheral Registers

PO, P1, P2, P3: Port register. 자세한 사항은 section 4 'I/O Ports'를 참고하기 바란다.

- TCON(0x88): Timer 0, 1 configuration register. 자세한 사항은 section 5.1 'Timer 0, 1'을 참고하기 바란다.

- TMOD(0x89): Timer 0, 1 control mode register. 자세한 사항은 section 5.1 'Timer 0, 1'을 참고하기 바란다.

- TH0(0x8C), TL0(0x8A): Timer 0의 Counter register. 자세한 사항은 section 5.1 'Timer 0, 1'을 참고하기 바란다.

- TH1(0x8D), TL1(0x8B): Timer 1의 Counter register. 자세한 사항은 section 5.1 'Timer 0, 1'을 참고하기 바란다.

- SCON(0x98): UART Configuration Register. 자세한 사항은 section 6 'UART'를 참고하기 바란다.

- SBUF(0x99): UART Buffer Register. 자세한 사항은 section 6 'UART'를 참고하기 바란다.

- **IE(0xA8)**: UART Bits in Interrupt Enable Register. 자세한 사항은 section 6 'UART'를 참고하기 바란다.

- IP(0xB8): UART Bits in Interrupt Priority Register. 자세한 사항은 section 6 'UART'를 참고하기 바란다.

- **TA(0xC7)**: Timed Access Register. 자세한 사항은 section 7 'Watchdog Timer'를 참고하기 바란다.

- **T2CON(0xC8)**: Timer 2 Configuration Register. 자세한 사항은 section 5.2 'Timer 2'를 참고하기 바란다.

- RLDH(0xCB), RLDL(0xCA): Capture Registers of Timer 2. 자세한 사항은 section 5.2 'Timer 2'를 참고하기 바란다.

- TH2(0xCD), TL2(0xCC): Counter Register of Timer 2. 자세한 사항은 section 5.2 'Timer 2'를 참고하기 바란다.

- PSW(0xD0): Program Status Word Register. 자세한 사항은 section 1.3.1. 'ALU'를 참고하기 바란다.

- WDCON(0xD8): Watchdog Control Register. 자세한 사항은 section 7 'Watchdog Timer'를 참고하기 바란다.

41

# 3 Interrupt

Interrupt pin 기능들을 아래 테이블에 정리하였다. 모든 pin들은 단방향성 (unidirectional) 이고, tri-state 신호는 없다.

Table 3.1 External Interrupt Pin Description

Active Type Pu/Pd Description

| Pin       | Active      | Туре | Pu/Pd | Description                            |

|-----------|-------------|------|-------|----------------------------------------|

| nINT0/FA6 | Low/Falling | I    | -     | External interrupt 0                   |

| nINT1/FA7 | Low/Falling | I    | -     | External interrupt 1                   |

| nINT2/FA8 | Falling     | I    | -     | External interrupt 2                   |

| nINT3/FA9 | Falling     | I    | -     | External interrupt 3                   |

| nINT4     |             |      | -     | Reserved                               |

| TCPIPCore | Falling     | I    | -     | Interrupt Request Signal for TCPIPCore |

| (nINT5)   |             |      |       | (internally connected)                 |

W7100A core는 두 level의 interrupt priority control을 갖고 있다. 각각의 외부 interrupt는 IP (0xB8)와 EIP(0xF8) register를 설정하거나 clear함으로써 high혹은 low level priority group으로 설정된다. 외부 interrupt pin들은 falling edge signal에 의해 activate된다. Interrupt request들은 system clock의 rising edge에서 sampling한다.

Table 3.2 W7100A Interrupt Summary

| Interrupt | Function                    | Active      | Flag Reset | Vector | Interrupt | Natural  |

|-----------|-----------------------------|-------------|------------|--------|-----------|----------|

| Flag      | Level/Edge                  |             |            |        | Number    | Priority |

| IE0       | Device pin INTO Low/Falling |             | Hardware   | 0x03   | 0         | 1        |

| TF0       | Internal, Timer0            | -           | Hardware   | 0x0B   | 1         | 2        |

| IE1       | Device pin INT1             | Low/Falling | Hardware   | 0x13   | 2         | 3        |

| TF1       | Internal, Timer1            | -           | Hardware   | 0x1B   | 3         | 4        |

| TI0 & RI0 | Internal, UART              | -           | Software   | 0x23   | 4         | 5        |

| TF2       | Internal, Timer2            | -           | Software   | 0x2B   | 5         | 6        |

| INT2F     | Device Pin INT2             | Falling     | Software   | 0x43   | 8         | 7        |

| INT3F     | Device Pin INT3             | Falling     | Software   | 0x4B   | 9         | 8        |

| INT4F     | Reserved                    |             |            |        |           |          |

| INT5F     | Interrupt for               | Falling     | Software   | 0x5B   | 11        | 10       |

| TCPIPCore | TCPIPCore                   |             |            |        |           |          |

| WDIF      | Internal,                   | -           | Software   | 0x63   | 12        | 11       |

|           | WATCHDOG                    |             |            |        |           |          |

각 interrupt 벡터는 IE (0xA8) 과 EIE (0xE8) register에서 해당 bit를 설정함으로써 각각 enable혹은 disable될 수 있다. IE register는 global interrupt system disable(0)/enable(1) bit

EA를 포함하고 있다.

#### IE (0xA8)

| 7  | 6 | 5   | 4  | 3   | 2   | 1   | 0   | Reset |

|----|---|-----|----|-----|-----|-----|-----|-------|

| EA | - | ET2 | ES | ET1 | EX1 | ET0 | EX0 | 0x00  |

Figure 3.1 Interrupt Enable Register

Note: EA - Enable global interrupt

EXO - Enable INTO interrupt

ETO - Enable TimerO interrupt

EX1 - Enable INT1 interrupt

ET1 - Enable Timer1 interrupt

ES - Enable UART interrupt

ET2 - Enable Timer2 interrupt

Interrupt를 enable하는 위의 모든 bit들은 software로 clear혹은 set할 수 있고, hardware로도 같은 결과를 얻을 수 있다. 즉, interrupt들은 software를 통해 생성될 수 있고 취소될 수도 있다 (단, IEO과 IE1 flag는 제외). 만약 외부 interrupt0, interrupt1이 level-activated로 program되어있다면, IEO과 IE1은 각각 외부 source pin nINT0/FA6과 nINT1/FA7을 통해 제어할수 있다.

#### IP (0xB8)

| 7 | 6 | 5   | 4  | 3   | 2   | 1   | 0   | Reset |

|---|---|-----|----|-----|-----|-----|-----|-------|

| - | - | PT2 | PS | PT1 | PX1 | PT0 | PX0 | 0x00  |

Figure 3.2 Interrupt Priority Register

Note: PXO - INTO priority level control (high level at 1)

PTO - TimerO priority level control (high level at 1)

PX1 - INT1 priority level control (high level at 1)

PT1 - Timer1 priority level control (high level at 1)

PS - UART priority level control (high level at 1)

PT2 - Timer2 priority level control (high level at 1)

Unimplemented bit - Read as 0 or 1

#### TCON (0x88)

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | Reset |

|-----|-----|-----|-----|-----|-----|-----|-----|-------|

| TF1 | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0 | 0x00  |

Figure 3.3 Timer 0, 1 Configuration Register

Note: ITO - INTO level (at 0)/edge (at 1) sensitivity

IT1 - INT1 level (at 0)/edge (at 1) sensitivity

- IEO INTO interrupt flag는 processor가 interrupt routine을 수행할 때 자동으로 clear된다.

- IE1 INT1 interrupt flag는 processor가 interrupt routine을 수행할 때 자동으로 clear된다.

- TFO Timer 0 interrupt (overflow) flag는 processor가 interrupt routine을 수행할 때 자동으로 clear된다.

- TF1 Timer 1 interrupt (overflow) flag는 processor가 interrupt routine을 수행할 때 자동으로 clear된다.

## SCON (0x98)

| 7   | 6   | 5   | 4   | 3   | 2   | 1  | 0  | Reset |

|-----|-----|-----|-----|-----|-----|----|----|-------|

| SM0 | SM1 | SM2 | REN | TB8 | RB8 | TI | RI | 0x00  |

Figure 3.4 UART Configuration Register

Note: RI - UART receiver interrupt flag

TI - UART transmitter interrupt flag

#### EIE (0xE8)

| 7 | 6 | 5 | 4    | 3     | 2     | 1     | 0     | Reset |

|---|---|---|------|-------|-------|-------|-------|-------|

| - | - | - | EWDI | EINT5 | EINT4 | EINT3 | EINT2 | 0x00  |

Figure 3.5 Extended Interrupt Enable Register

Note: EINT2 - Enable external INT2 Interrupt

EINT3 - Enable external INT3 Interrupt

EINT4 - Must be '0', if use the EIE register

EINT5 - Enable TCPIPCore Interrupt

EWDI - Enable WATCHDOG Interrupt

#### EIP (0xF8)

| 7 | 6 | 5 | 4    | 3     | 2     | 1     | 0     | Reset |

|---|---|---|------|-------|-------|-------|-------|-------|

| - | - | - | PWDI | PINT5 | PINT4 | PINT3 | PINT2 | 0x00  |

Figure 3.6 Extended Interrupt Priority Register

Note: PINT2 - INT2 priority level control (high level at 1)

PINT3 - INT3 priority level control (high level at 1)

PINT4 - Must be set to '0', if use the EIP register

PINT5 - TCPIPCore Interrupt priority level control (high level at 1)

PWDI - WATCHDOG priority level control (high level at 1)

#### EIF (0x91)

| 7 | 6 | 5 | 4 | 3     | 2     | 1     | 0     | Reset |

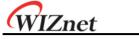

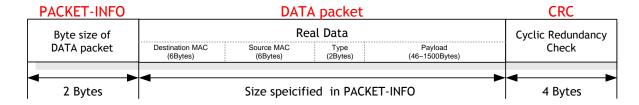

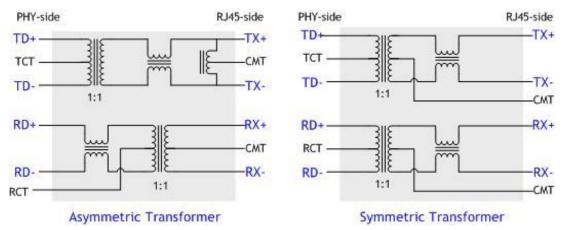

|---|---|---|---|-------|-------|-------|-------|-------|